四種常用FPGA/CPLD設計思想與技巧之流水線操作

本系列討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

FPGA/CPLD 的設計思想與技巧是一個非常大的話題,由于篇幅所限,本文僅介紹一些常用的設計思想與技巧,包括乒乓球操作、串并轉換、流水線操作和數據接口的同步方法。希望本文能引起工程師們的注意,如果能有意識地利用這些原則指導日后的設計工作,將取得事半功倍的效果!

流水線操作設計思想

首先需要聲明的是,這里所講述的流水線是指一種處理流程和順序操作的設計思想,并非FPGA、ASIC設計中優化時序所用的“Pipelining”。

流水線處理是高速設計中的一個常用設計手段。如果某個設計的處理流程分為若干步驟,而且整個數據處理是“單流向”的,即沒有反饋或者迭代運算,前一個步驟的輸出是下一個步驟的輸入,則可以考慮采用流水線設計方法來提高系統的工作頻率。

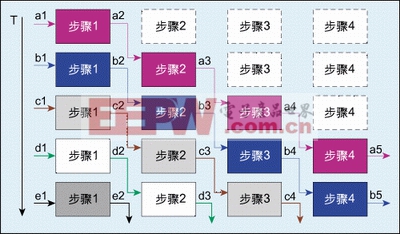

流水線設計的結構示意圖如圖1所示。其基本結構為:將適當劃分的n個操作步驟單流向串聯起來。流水線操作的最大特點和要求是,數據流在各個步驟的處理從時間上看是連續的,如果將每個操作步驟簡化假設為通過一個D觸發器(就是用寄存器打一個節拍),那么流水線操作就類似一個移位寄存器組,數據流依次流經D觸 發器,完成每個步驟的操作。流水線設計時序如圖2所示。

流水線設計的一個關鍵在于整個設計時序的合理安排,要求每個操作步驟的劃分合理。如果前級操作時間恰好等于后級的操作時間,設計最為簡單,前級的輸出直接匯入后級的輸入即可;如果前級操作時間大于后級的操作時間,則需要對前級的輸出數據適當緩存才能匯入到后級輸入端;如果前級操作時間恰好小于后級的操作時 間,則必須通過復制邏輯,將數據流分流,或者在前級對數據采用存儲、后處理方式,否則會造成后級數據溢出。

在WCDMA設計中經常使用到流水線處理的方法,如RAKE接收機、搜索器、前導捕獲等。流水線處理方式之所以頻率較高,是因為復制了處理模塊,它是面積換取速度思想的又一種具體體現。

評論