基于ARM和W5100的嵌入式以太網通信接口設計

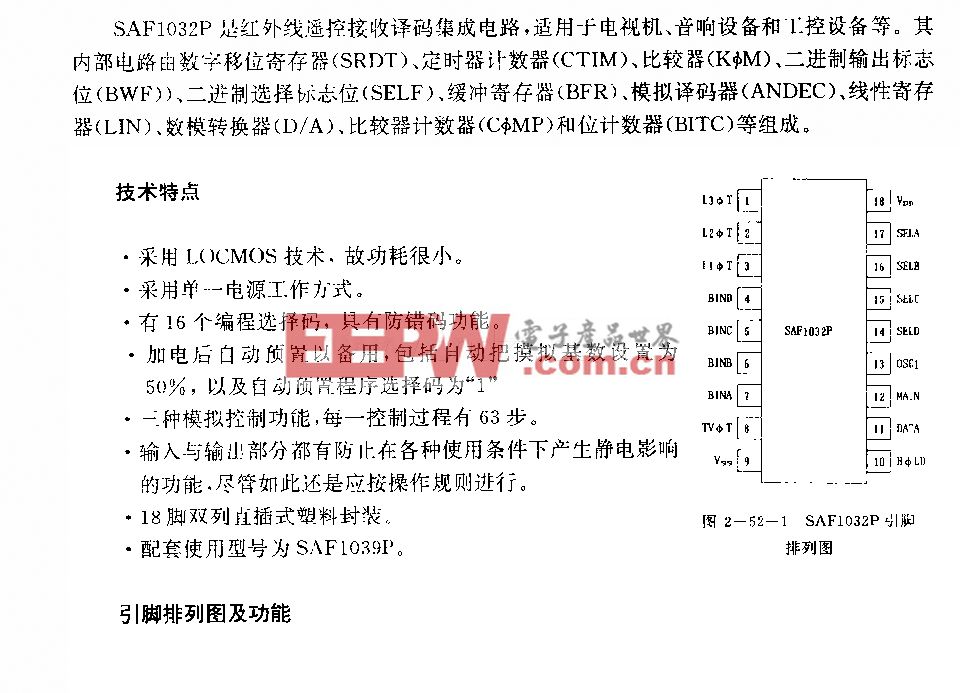

隨著以太網技術在工業遠程監控和數據采集領域的飛速發展,基于以太網的應用接口設備也迅速普及到醫療設備、工廠電力系統等應用。然而,嵌入式以太網接口設計的核心器件是網絡控制芯片,其性能優劣直接影響網絡通信的效率。

本文結合ARM技術,采用32 bit STM32F105V微處理器和高性能的以太網控制芯片W5100實現高性能、高可靠性的嵌入式以太網通信接口設計,其系統各功能模塊容易擴展和升級。

1 總體設計

在嵌入式系統設計高速發展的過程中,與傳統的基于現場總線方式相比,結合嵌入式系統和以太網技術來實現數據采集和控制功能越來越受到廣大嵌入式設計者的青睞,而通信接口設計實質是能夠實現TCP/IP網絡通信協議。使用本接口模塊的核心控制器W5100,應用程序設計者無需深入了解TCP/IP協議,也無需考慮以太網的控制,只需訪問網絡控制器的寄存器,并靈活創建和選擇TCP及UDP套接字(Socket)函數就可以簡單地實現網絡通信,且不需要操作系統的支持,其具有硬件電路簡單、編程方便等特點,解決了一般嵌入式設計的軟件設計復雜、網絡編程工作量大等問題,再結合32 bit高性能ARM處理器以真正實現以太網的高速實時傳輸。ARM完成對應用程序的處理,W5100實現數據傳輸和通信網絡協議的處理。

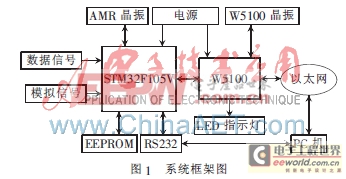

具體實現過程:數據信號或模擬信號可以通過STM32F105V豐富的外設接口(RS232總線、CAN總線等)輸入或直接通過外部數據總線輸入,并且可以用ARM處理器對傳輸的數據和信號做一些預處理工作,然后傳輸到W5100芯片完成網絡協議的處理,再通過網絡接口傳輸到遠程終端(PC機)。相反,遠程終端可以通過以太網發出控制指令,將傳輸信號發送至ARM或數據輸出端,從而實現嵌入式系統中網絡數據的采集和傳輸控制。系統框架如圖1所示。

本設計利用JTAG接口燒寫程序到ARM內部的Flash,外擴I2C接口的128×8(1 Kbits)EEPROM,基地址為Ox40005400,用來存儲網絡IP地址、端口號、子網掩碼等網絡信息,網絡傳輸狀態指示燈(LED)反映了數據傳輸的實時狀態。電源由外部電源提供,分別經過MC7805和AS1117芯片穩壓轉換輸出5 V和3.3 V的電壓,這樣就能夠很好地滿足內核、外設以及外部電路的供電[1]。

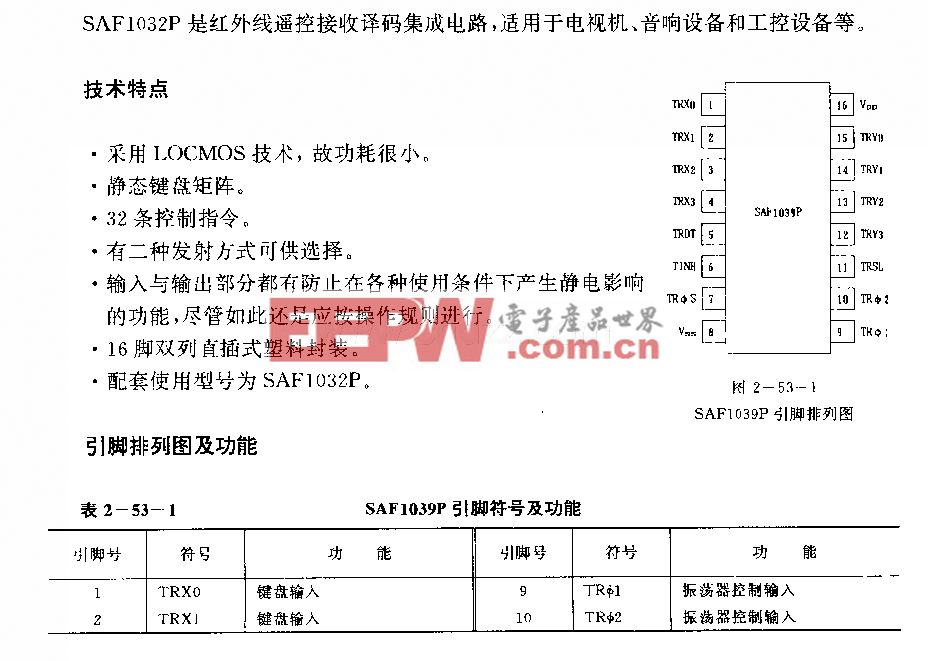

2 網絡控制器W5100

W5100是WIZnet公司最新推出的固件網絡芯片,內部集成了10/100 Mb/s以太網控制器,支持自動應答(全雙工/半雙工模式),最高通信速率達25 Mb/s。W5100將TCP/IP協議棧、以太網MAC和PHY三種功能集成于一體,支持硬件化的TCP、UDP、ICMP、IPv4 ARP、IGMP、PPPoE、以太網等協議,并提供了多種總線接口方式(直接總線接口、間接總線接口、SPI總線)便于連接各類單片機,可以滿足不同應用場合的需求。

W5100內含公共存儲器、端口存儲器、發送存儲器以及接收存儲器。公共寄存器用來設置W5100的工作模式、中斷向量、IP地址、網關地址、子網掩碼、物理地址、超時值等相關信息;端口寄存器平均分為4個相等的存儲器大小,可以單獨對4個獨立的網絡通道(Socket)設置端口的通信模式(TCP客戶端模式、TCP服務器模式、UDP模式),實現網絡數據的通信;內部16 KB存儲器的發送和接收數據緩沖區(8 KB的發送緩存和8 KB接收緩存區)用來存放臨時數據。W5100支持ADSL連接(支持PPPoE協議、帶PAP/CHAP驗證),支持自動極性變換(MDI/MDIX)并附帶有多功能LED指示燈輸出,時鐘信號由外部晶振25 MHz提供,分別接入XTLP、XTLN管腳。

W5100支持80腳的LQFP小型封裝,0.18 μm CMOS工藝,符合環保要求。3.3 V的單電源工作電壓,I/O口可承受5 V電壓,可以滿足低功耗要求[2]。

3 通信接口硬件設計

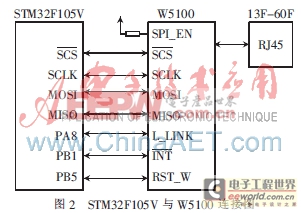

本設計采用嵌入式微處理器和以太網控制器的方式實現接口轉換,需要用到的芯片主要包括STM32F105V微處理器,W5100網絡控制器及帶網絡變壓器的RJ-45接口13F-60系列,AT24LC01B EEPROM等。采用SPI總線接口模式,實現STM32F105V和網絡控制器的硬件連接。在串行接口模式下,只需要連接幾個簡單的引腳就可以進行數據通信[3]。SPI總線接口模式下硬件連接如圖2所示。

本系統微處理器采用ST公司的STM32F105V,并采用專門設計的Cortex-M3內核,時鐘頻率可達72 MHz,256 KB Flash存放程序或數據,64 KB的RAM存放數據,多達80個I/O接口可以映射到20個外部中斷。STM32F105V與W5100供電電壓都是3.3 V,所以可以直接連接。

配置W5100的SEN引腳必須通過一個10 kΩ的電阻接高電平,以選擇W5100的SPI接口模式,置STM32F105V為SPI主模式,W5100為SPI從模式,在SPI總線模式下的配置復用輸入輸出接口(AFIO)的PA5、PA6、PA4、PA7分別為SCLK、MISO、/SCS(SPI從模式選擇,低電平有效)、MOSI信號線直接相連,并用軟件設置管腳的輸出最大速度為10 MHz,STM32F105V通過SPI對W5100讀寫操作。

配置PB5口作為W5100的復位信號/RST_W,低電平有效。為實現準確的硬件復位,復位引腳RST_W上復位信號至少保持2 μs。

配置PB1口為外部中斷線1(EXTI1),并作為W5100的中斷信號輸出端/INT,低電平有效。當W5100在端口產生連接、斷開、接收數據、數據發送完成以及通信超時等條件下,該引腳輸出低電平信號指示微處理器。

配置PA8口為W5100輸出的以太網物理層信號燈(LINKLED)指示W5100的網絡連接狀態,通過上拉電阻輸入到微處理器,低電平有效。

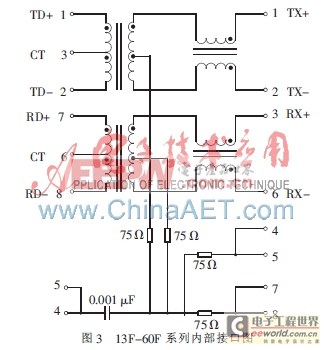

此外,為縮小接口設計的面積,本設計采用10/100 Mb/s的13F-60系列帶網絡變壓器的RJ45接口,W5100的RXIP接RJ45的RD+,RXIN接RD-,并帶有左右兩個狀態燈,連接狀態燈(LINKLED)和動態指示燈顯示接收與發送狀態(ACT_LED),通過一個高速開關二極管共陽極(開關速度最大值4 ns,重復反向峰值耐壓最大值75 V)與W5100的RXLED/TXLED管腳相連,供電電壓為3.3 V,直接與W5100相連。差分接收和發送引腳分別通過兩個75 Ω的電阻和0.001 μF的電容接地。RJ45接口的內部結構圖如圖3所示。

4 通信接口的軟件設計

4.1 初始化程序設計

本系統初始化通過定義結構體的方式完成STM32F105V微處理器和W5100的初始化[4-5]。

微處理器完成系統時鐘、外設時鐘、系統啟動模式、嵌入式向量式中斷控制寄存器、I2C、通用輸入輸出接口、通用異步接收發送器、通用定時器以及SPI等的初始化。

W5100的初始化主要設置一些關鍵的寄存器:

(1)設置模式寄存器(MR)bit[7](軟件復位位)為1,初始化芯片內部寄存器,復位后自動清0。

(2)設置中斷屏蔽寄存器(IMR)為OxFF(屏蔽中斷源),啟動IP地址沖突異常中斷和端口n寄存器(Sn_INT)中斷等,通過向相應的中斷屏蔽位寫1,任何時候只要中斷寄存器(IR)對應的位也置1,則中斷將產生,CPU通過訪問IR獲得中斷來源。

(3)設置重發時間寄存器(RTR)為200 ms(Ox07D0),當發出連接、斷開等命令而沒有收到遠程對端的響應或響應延遲時,產生重發過程。

(4)配置重發計數寄存器(RCR)為8,設定重發的次數。

(5)設置接收緩沖區的大小寄存器(RMSR)和發送存儲空間大小寄存器(TMSR)都為0x55,每個端口接口和發送存儲空間分別分配2 KB的存儲空間。

(6)設置端口n模式寄存器(Sn_MR)為OxA1,啟動廣播功能,設置端口n協議類型為TCP模式。

(7)設置端口n命令寄存器(Sn_CR),端口的初始化、建立/斷開連接以及數據傳輸等。

(8)設置端口n的最大分片長度寄存器(Sn_MSS)為1 460。

初始化完成后,根據SPI協議編寫發送字節函數SPI_SendByte(),配合Read_W5100和Write_W5100完成字節的讀取和發送,這里需要定義讀操作碼(OxF0)和寫操作碼(Ox0F),實現微處理器與W5100數據通信。

4.2 Socket初始化程序設計

W5100與終端之間的數據交換有多種通信方式,本文采用基于TCP模式的通信方式。TCP是以連接為基礎的通信方式,端口n在進行數據通信時,必須先建立連接。TCP有兩種建立連接方式,一種是服務器模式(被動模式),需要等待連接請求;另一種是客戶端模式(主動打開),需要發送連接請求給服務器。本設計配置W5100為服務器模式,只需對W5100的Socket進行配置就可以完成網絡數據的收發和啟動功能。

當Socket作為服務器模式時,初始化端口需要設置運行模式(Sn_MR)和本機端口號(Sn_Port),并在端口命令寄存器打開(OPEN)端口。引用Socket_Listen(SOCKET s)程序,只調用一次該程序就可使W5100設置為服務器模式。主要程序如下所示。

Write_W5100((W5100_S0_MR+s*0x100),S_MR_TCP);

//設置Socket為TCP模式

Write_W5100((W5100_S0_CR+s*0x100),S_CR_OPEN);

//打開Socket

Write_W5100((W5100_S0_CR+s*0x100),S_CR_LISTEN);

//設置Socket為偵聽模式

Write_W5100((W5100_S0_CR+s*0x100),S_CR_CLOSE);

//關閉Socket

完成Socket的打開和設置偵聽工作后,至于遠程客戶端是否與其連接,則需要等待Socket中斷,在服務器偵聽模式下,不需要設置目的IP和目的端口號。

W5100在TCP服務器模式下的處理流程如圖4所示。

4.3 中斷處理程序設計

本設計采用中斷方式來處理數據包的接收和發送,以提高效率。在W5100處理中斷的過程中,微處理器首先通過應訪問W5100的中斷寄存器(IR)獲得產生中斷的來源。中斷寄存器與中斷屏蔽寄存器配合使用,且位是一一對應的,中斷屏蔽寄存器(IMR)的相應位可屏蔽中斷寄存器中任何中斷源。因此,若要使用某個中斷源,先要將該中斷源在中斷屏蔽寄存器中的相應位置位,以打開所需的中斷源,這樣,中斷才會產生。當中斷產生后,即進入中斷處理程序。本設計中的中斷源主要包括端口n中斷事件。一般設置有Socket成功連接(S_IR_CON)、斷開連接(S_IR_DISCON)、數據發送完成(S_IR_SENDOK)、接收到數據(S_IR_RECV)或傳輸超時(S_IR_TIMEOUT)等事件中斷。

本文以端口0接收到數據包后的產生一個接收數據中斷為例說明中斷處理過程。首先,在使用端口0中斷之前,應在初始化程序中將中斷屏蔽寄存器(IMR)中的端口0置位(IMR_S0_INT),當Socket0發生中斷時,IMR_S0_INT=1、IR_S0_INT=1、動態LED燈亮顯示接收狀態,此時,W5100的中斷輸出管腳(/INT)輸出低電平,以通知微處理器有中斷產生,微處理器訪問中斷寄存器獲取中斷源為接收數據中斷;然后進入中斷處理函數,啟動發送函數(S_rx_process)。

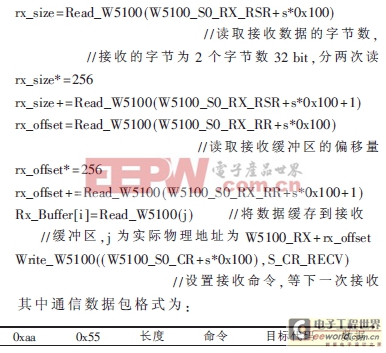

4.4 Socket數據接收程序設計

當端口接收數據時,產生接收中斷。首先調用端口接收數據包函數Process_Socket_Data(),并對接收到的數據類型進行判斷和加工。本過程先調用接收函數S_rx_process()從W5100端口的接收數據緩存區讀取數據,然后將讀取的數據加上接收存儲器讀指針寄存器(S0_RX_RD)的值再寫入S0_RX_RD,最后將RECV命令重新寫入端口0的命令寄存器(S0_CR),以等待下次數據的接收。或者將處理完的數據拷貝到發送緩沖區,再調用S_tx_process函數發送數據包給CPU。主要程序如下:

其中Oxaa和Ox55為接收數據包的標志頭;長度位為數據包字節長度,不包括數據包頭和本身字符,命令位為對對象數據的操作,為0時讀取數據,為1時設置對象數據,目標代碼位用來顯示對象代碼,如Ox00為網關IP、Ox01為子網掩碼、0x02為物理地址、LED為狀態顯示等;數據位為接收到的數據,數據是以16進制形式接收,最后再加上2 B的數據報頭和1 B的數據本身。

4.5 Socket數據發送程序設計

通過Socket發送數據時,調用發送數據函數S_tx_process。首先把要發送的數據緩存在發送緩沖區(Tx_buffer)中。此外,在發送數據時,需先檢查發送緩存區的剩余空間的大小(Sn_TX_FSR),控制發送數據的字節數,如用以太網協議發送的數據最大傳送單元(MTU)不超過1 500 B。在TCP服務器模式下,在數據發送處理過程中,可不設置目標主機的IP和端口號。剩余空間的大小因寫入數據的增加而減少,數據發送后又自動增加。當發送緩沖區的數據完全寫入端口的發送數據緩存區后,則將數據本身長度加上端口傳輸寫指針寄存器(Sn_TX_WR)中的值再寫入Sn_Tx_WR,再計算發送緩沖區的偏移量(tx_offset),用于指示發送數據的長度,最后啟動發送(Sn_CR_SEND)。相關程序如下:

i=tx_offset/S_TX_SIZE //計算實際物理偏移值,

//S_TX_SIZE由TMSR定義為2 K

tx_offset=tx_offset-i*S_TX_SIZE //計算實際物理地址

//j= W5100_TX+s*S_TX_SIZE+tx_offset

Write_W5100(j,Tx_Buffer[i]) //將發送緩沖區中的

//數據寫入到端口的發送緩沖區

Write_W5100((W5100_S0_CR+s*0x100),S_CR_SEND)

//啟動發送的指令

本文以基于ARM Cortex-M3的微處理器STM32F105V為核心,結合W5100網絡控制芯片實現了嵌入式以太網的連接,該接口設計具有硬件設計簡單、成本低、集成高度以及軟件開發周期短等優點,在自動化控制和數據傳輸領域有著廣泛的市場和應用前景。

參考文獻

[1] ST.STM32F105xx datasheet.2010.

[2] WIZnet.W5100 datasheet version1.1.8. 2009.

[3] 姚冰,康世英,謝佳.嵌入式以太網接口硬件部分的設計與實現[J].微處理機,2008,29(2):155-157.

[4] 成都加聯科技有限公司.W5100在嵌入式系統中實現TCP/IP網絡通信的應用[R].2009.

[5] 段海龍,彭輝俊,程健.基于ARM的嵌入式以太網通信的實現[J].機械與電子,2006(2):9-12.

tcp/ip相關文章:tcp/ip是什么

存儲器相關文章:存儲器原理

上拉電阻相關文章:上拉電阻原理

評論