基于DSP E1—16XS的硬件開發平臺設計

引 言

嵌入式系統硬件的核心是各種類型的嵌入式處理器,目前全世界嵌入式處理器的品種已經超過1000多種,流行體系結構有30多個系列。嵌入式處理器一般可以分為嵌入式微處理器、嵌入式微控制器、嵌入式DSP處理器和嵌入式片上系統。

與標準微處理器相比,嵌入式微處理器只保留了和嵌入式應用有關的功能,并且為了滿足嵌人式應用的特殊要求,在工作溫度、抗電磁干擾、可靠性等方面都做了各種增強。

DSP嵌入式系統是DSP系統嵌人到應用電子系統中的一種通用系統。這種系統既具有DSP器件在數據處理方面的優勢,又具有應用目標所需要的技術特征。在許多嵌人式應用領域,既需要在數據處理方面具有獨特優勢的DSP,也需要在智能控制方面技高一籌的微處理器(MCU);因此,將DSP與MCU融合在一起的雙核平臺,將成為DsP技術發展的一種新潮流。德國Hyperstone公司是真正把DSP成功嵌入32位微處理器的廠商之一,尤其是它的E1一XS系列更是這方面的佼佼者。

1 E1-16XS微處理器結構概述

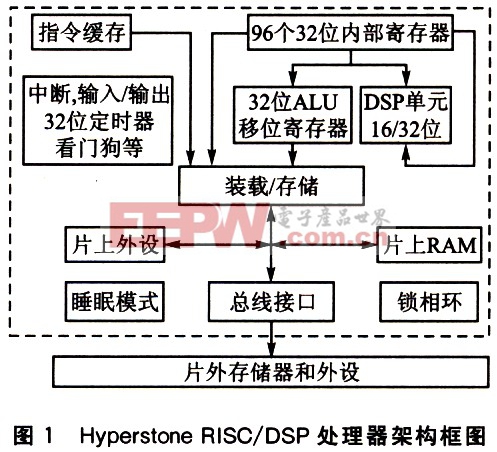

Hyperstone RISC/DSP架構框圖如圖1所示。

Hy—perstone內核是專為RISC和DSP功能的集成而設計的,但它不是兩個不同內核在單個芯片上的簡單組合,而是一個集成的內核和指令集。這一全集成的內核基于單處理器模式,帶有單指令流。RISC和DSP單元間簡單且高效的通信由1個96路的32位內部寄存器實現,在每個時鐘周期內可以執行3條指令的操作。所以在100 MHz的頻率下可以達到3。O MOPS這樣優秀的性能。

Hyperstone E1-16xS是一款O.25μm CMOS工藝的微處理器。它結合了高性能的RISC微處理器和DSP處理器,利用簡潔高效的指令,使嵌入式DSP處理器的實時性得以充分的發揮。

該處理器主要具有如下的特點:

①32位RISC/DSP處理器,ALU、DSP單元和LoaoI/Store單元并行處理,內部集成硬件乘法器。

②16根數據線,22根地址線,4個外部存儲體(Mem—oryr Bank)選擇信號。

③4 GB內存地址空間,I/O空間和存儲空間分開尋址,存儲器和DSP連接無需附加邏輯電路。

④片內集成16 KB RAM和片上指令高速緩存。⑤具有全面的DRAM和DMA控制器,所有的總線時序可編程。

⑥片上PLL、CPU最高頻率可達180 MHz。

⑦中斷服務程序可在7個時鐘周期內啟動。除內部中斷外,還有7個外部中斷可用。

⑧3個可編程I/O引腳除了可配置成輸入輸出外,還可以配置成外部中斷輸入使用。

⑨32位定時器和看門狗定時器;用戶可利用hyRTK內核訪問154個獨立的“虛擬”定時器,僅需很少的處理開銷。

2 嵌入式系統硬件設計

2.1 系統硬件結構

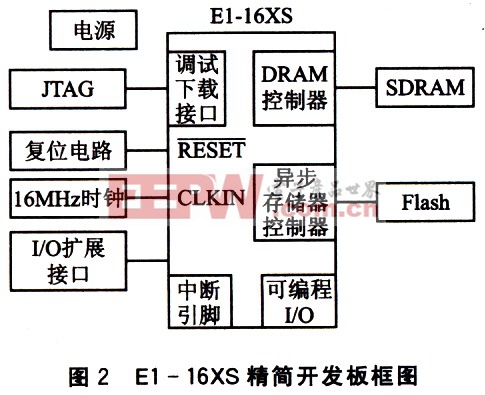

系統硬件結構如圖2所示

電源電路:輸入5 V,經過DC-DC變換,分別給微處理器提供2.5 V和3.3 V的電壓。

晶振電路:16 MHz有源晶體振蕩器經過倍頻,分別為Hyperstone內核/系統提供128/64 MHz的時鐘頻率。

復位電路:可選用簡單的RC復位電路,考慮到系統復位的可靠性和掉電監控,建議使用專門的復位IC,例如MAX706。

微處理器:即E1-16XS,是系統的工作和控制中心。

Flash:可存放Boot監控程序、嵌入式操作系統、用戶應用程序或其他在系統掉電后需要保存的數據。

SDRAM:系統代碼運行和數據變量存儲的空間。

JTAG接口:通過該接口可對系統進行在線調試和程序下載。

I/O擴展接口;引出數據總線、地址總線和必需的I/0控制總線,便于用戶根據自身的特定需求,擴展外圍電路;DSP可以通過該擴展總線對其他板卡進行控制,或者其他板卡可以通過該接口對開發板進行操作。

2.2 系統主要硬件單元電路設計

不同的DSP處理器在與DRAM、Flash連接時通常會有些差異,所以下面著重分析存儲器接口電路的工作原理和設計方法。

(1)Flash接口電路

由于Flash存儲器具有低功耗,大容量,可整片或分扇區快速燒寫、擦除,掉電后信息不丟失等特點,在各種嵌入式系統中得到廣泛應用。

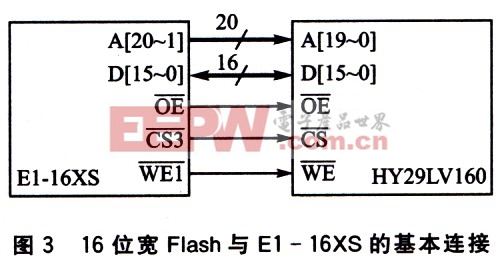

本系統中,Flash存儲器采用Hynix的HY29LV160。它是16位數據寬度,存儲容量為16 Mb(2 MB),可以在2.7~3.6 V電壓范圍內進行讀、編程(燒寫)和擦除操作。

在大多數系統中,選用1片16位的Flash存儲器芯片(單片容量有1 MB、2 MB、4 MB、8 MB等)構建16位的Flash存儲系統已經足夠。在此采用1片HY29LV160構建16位的Flash存儲器系統。圖3為16位模式Flash與處理器E1—16XS的基本接法。

Flash存儲器在系統中通常用于存放程序代碼、系統上電或復位后從此獲取指令并開始執行。因此,應將存有程序代碼的Flash存儲器配置到Bank3,即將E1—16XS的CS3接至HY29LV160的片選端CE。輸出使能端面OE接E1- 16XS的OE;寫使能端WE接E1—16XS的WEl模式選擇BYTE上拉,使HY29LV160工作在16位數據模式;RY/BY(就緒/忙)指示HY29LV160編程或擦除操作的工作狀態。

HY29LV160地址總線A[19~O]與E1-16XS的地址總線A[20~1]相連;16位數據總線D[15~0]與El一16XS的16位數據總線D[15~o]相連。此時應將E1—16XS的B00TB置為O,即選擇外部F1ash為16位工作方式。

(2)DRAM接口電路

與Flash存儲器相比較,動態隨機存儲器DRAM雖然不具有掉電保持數據的特性,但其存取速度大大高于Flash存儲器,在系統中主要用作程序的運行空間。

E1-16XS內部的DRAM控制器支持DRAM的各種形式,例如Fast—Page Mode,、EDO和SDRAM,都可以直接和處理器無縫連接。存儲器存取的總線時序刷新控制等可由總線控制寄存器(BCR)設定。這里以目前嵌入式系統設計中常用的SDRAM說明電路的具體連接。

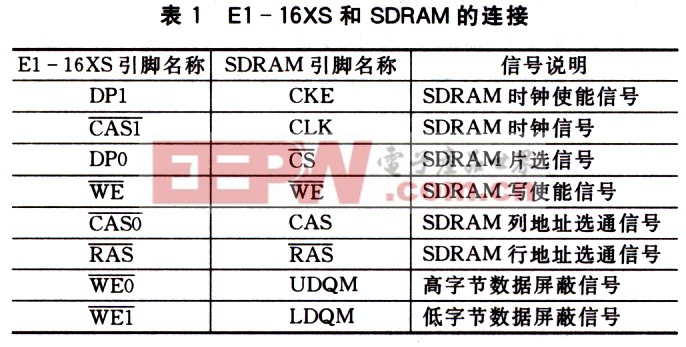

系統中SDRAM選用IS42S16100一7T。它的存儲容量為2 BatLks×512 K×16位(2 MB),工作電壓為(3.3±0.3)V,16位數據寬度。如果用戶需要運行嵌入式操作系統及各種相對較復雜的功能,可以考慮增加SDRAM的容量。E1—16XS最大支持128 MB。

圖4為IS42S16l。

0—7T SDRAM存儲器和El一。16XS的連接框圖。將該SDRAM配置到系統存儲器的Bank0,即將E1—16XS的DP0(SDRAM選擇信號)接至IS42S16100的CS端。表l可以清晰地反映出El一16XS和IS42S16100的連接情況。

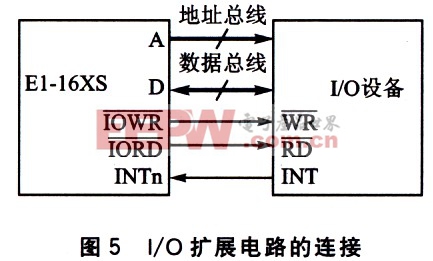

(3)I/O擴展

由于DSP本身的I/O口相對比較少,在很多應用場合下,需要進行I/O擴展。E1 16XS內部I/O總線控制寄存器提供了6位作為芯片選擇用,也就是可以連接64個周邊器件;另外還有3位作為I/O器件內部寄存器地址尋址用,9位用來設定讀寫訪問的總線時序設置,例如地址建立時間和保持時間等。這樣可以降低對外設的訪問速度,適應低速外設的要求。一般對外設I/O的訪問連接如圖5所示。

圖5中,IORD和IOWR為I/O訪問時的讀控制信號和寫控制信號,分別連接到I/O設備的讀和寫控制端;I/0設備的中斷輸出信號INT連接到DSP的中斷輸入信號INTn。E1—16XS提供了最多7個外部中斷輸入可供連接。

3 PCB板設計要點

設計好電路圖后,就可以設計PCB板了。在系統中,E1-16XS的片內工作頻率可以達到150 MHz以上,系統總線頻率也接近1OOMHz,因此,在PCB設計過程中,應該遵循高頻電路設計的基本原則。首先應注意電源的質量與分配,其次要注意信號線和時鐘線的分布。

(1)電源質量與分配

在設計PCB板時,給各個單元電路提供高質量的電源,會使系統的穩定性大幅度提高。一般應在電源進入印刷電路板的位置和靠近各器件的電源引腳處加上幾十~幾百μF的電容,以濾除電源噪聲。還要注意在器件的電源和地之間加上0.0l μF~O.1μF左右的電容,用來濾除元器件工作時產生的高頻噪聲。由于雙面PCB板電源采用電源總線的方式,受到電路板面積的限制,一般存在較大的直流電阻,所以為了提高系統的穩定性,通常采用多層板。一般專門拿出兩層,作為電源層和地層,而不在其上布信號線。低阻抗的電源層也可以像地層一樣作為高頻信號的返回通路,可以有效地降低噪聲。

(2)同類型信號線的分布

在設計PCB時,對于處理器的輸入輸出信號中的數據線、地址線等相同類型的線應該成組、平行分布,并保持它們之間的長短差異不要太大。采用這種方式布線,既可以減少干擾,增加系統的穩定性,還可以簡化布線,使PCB板的外觀美觀。

(3)時鐘信號線的分布

較高頻的時鐘信號是電路板的關鍵信號,頻率越高的時鐘其布線要求也越高。布線時應使時鐘源到負載的連線盡量短,線應盡量寬。不同時鐘之間、時鐘與其他信號之間避免平行走線。信號負載較多時,在一個驅動器上不要驅動其他時鐘信號,保證時鐘信號的質量良好。

結 語

該精簡開發板具有最小化的功能,用戶僅僅需要在Flash里預先燒寫Boot監控程序,就可以進行應用程序的調試和下載。該開發板具有良好的擴展性,通過I/O擴展接口為用戶的硬件擴展提供了很大的便利。用戶可以在不更改Boot監控程序的前提下對該精簡開發板進行硬件功能(串口、USB、可編程器件等)的擴充。

p2p機相關文章:p2p原理

評論