FPGA與外部存儲設備的接口實現

|

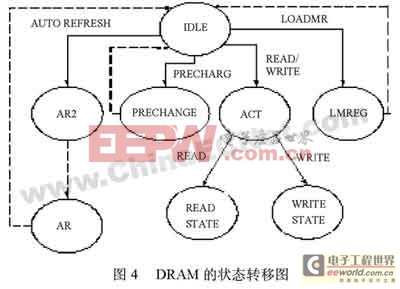

其次,是如何控制DRAM的各種狀態。當設計FPGA與DRAM的接口時,由于它除了讀寫狀態外還有較多的其它狀態,所以需要著重設計好讀寫狀態與其它狀態之間的轉換控制。為了解決這個問題,本設計采用了狀態機來控制這些狀態之間的關系,DRAM的狀態轉移圖如圖4所示:

下面給出了圖中各個狀態所表示的意思:

IDLE 表示存儲器處于空閑狀態;

LMREG 表示加載寄存器狀態;

ACT 表示活動狀態;

AR2 表示自動刷新有效狀態;

AR 表示自動刷新無效狀態;

WRITE STATE 表示讀狀態;

READ STATE 表示寫狀態;

只有當系統時鐘的上升延到來時,才會觸發這個狀態機改變一次當前狀態。

|

剛開始時,存儲器的初始狀態為空閑狀態,當有請求來時才會進入下一個狀態,如果沒有請求就一直保持空閑狀態。虛線表示自動按順序進入下一個狀態。

最后,是FPGA的設計要求。一個優秀的FPGA設計不僅要達到系統的基本要求,同時必須滿足可讀性、可重復性和可測性。

可讀性好的FPGA設計原理圖和硬件描述語言設計應該包含足夠詳細的注釋。每張原理圖之間的關系及硬件描述模塊間的互聯關系的說明固然重要,但是每個模塊本身的說明也是不能忽視的,例如狀態機的文檔應當包括狀態圖或功能描述。好的文檔也許花不了很多的時間,但是卻可以在調試﹑測試和維護設計上節省大量的時間。

可重復性指FPGA設計應該保證如果不同的人從不同的部位開始,并重新進行布局布線等,應該得到同樣的結果。沒有這個保證,驗證以及其他形式的設計測試就毫無意義。設計者顯然不希望在設計里出現這樣的情況,具有相同的輸入輸出管腳和功能的器件,由于布局布線的差異,導致最后時序不一致。如果在實現的過程中,系統設計軟件的參數或選項不一致,就會發生這種情況。因此FPGA的文檔就應該包括必要的信息,即軟件開發系統的版本號﹑軟件的各個選項及參數設計。

可測性是FPGA設計的最后一個特征。系統級的測試要求設計者對整個設計流程及系統架構都要很清楚。隨著設計層次的提高,使得設計者面對的電路規模越來越大,功能越來越復雜,相應電路的測試也變得越來越困難。在設計過程中綜合考慮測試的設計問題并統一實施,將有效地縮短整個產品的開發時間、減少返工。

結束語

在開發過程中由于采用高級硬件編程語言-編程器件的設計實現過程,大大縮短了開發周期,增加了硬件設計的靈活性和可移植性,也避免了專用集成電路設計的高風險。采用邏輯仿真與后時序仿真相結合的驗證方法,可以保證設計的可靠性。基于上述優點,這種開發方式在中小型集成電路開發中已得到廣泛應用。 隨著工藝技術的發展與市場的需要,超大規模﹑高速﹑低功耗的新型FPGA將會不斷推陳出新。現在新一代的FPGA甚至集成了中央處理器(CPU)或數字處理器(DSP)內核,在一片FPGA上進行軟硬件協同設計,為實現片上可編程系統(SOPC,System On Programmable Chip)提供了強大的硬件支持。

評論