基于FPGA NiosII的MPEG-4視頻播放器設計

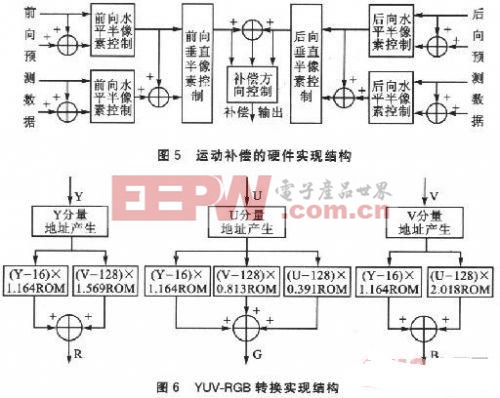

運動補償模塊的控制很復雜。實際設計時將它分成幾個子模塊:補償控制、補償?shù)刂樊a生、差分數(shù)據(jù)提供以及補償運算。這幾個子模塊直接采用硬件邏輯設計,運行時無需NiosII處理器干預。其中補償控制是完成整個運動補償?shù)目刂疲峁┹斎肟刂菩盘枴⑤敵隹刂菩盘枴⒕彺婵刂菩盘枴㈩A測數(shù)據(jù)和差分數(shù)據(jù)等;補償?shù)刂樊a生用于生成預測數(shù)據(jù)在幀緩存中的地址及補償結果的寫地址;差分數(shù)據(jù)負責接收IDCT的結果,通過緩存在適當時機提供補償使用;補償運算則完成最終預測數(shù)據(jù)的計算。

2.1.4 YUV-RGB轉換

根據(jù)YUV到RGB色彩空間的轉換關系,對每個乘積項都預先做出結果,存放在ROM當中。對每一個YUV分量的輸入,由硬件邏輯產生存取地址,并進行加法運算,從而得到對應的結果。其實現(xiàn)結構如圖6所示。

2.2 系統(tǒng)軟件工作流程

本系統(tǒng)的軟件工作流程如圖7所示。

結 語

該系統(tǒng)采用基于Altera FPGA嵌入式NiosII軟核的SOPC平臺實現(xiàn),具有較低的硬件成本,IP核的大量使用,良好的系統(tǒng)擴展性的特點。

評論