基于TMS320C64x 的MPEG-4實時編碼器設計與實現

MPEG-4算法非常復雜,其編解碼的實時性難以保證,通常只能實現對中低分辯率視頻的實時編碼。本文基于TI公司的C64x系列DSPs設計并實現了一種MPEG-4編碼器,實現了對D1分辨率(720×576)視頻的實時編碼,且在保證輸出碼率低于1Mbps的同時,解碼圖像具有較高的峰值信噪比和較好的視覺效果。

1 編碼系統的硬件結構

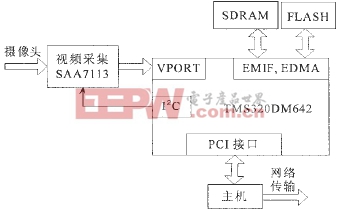

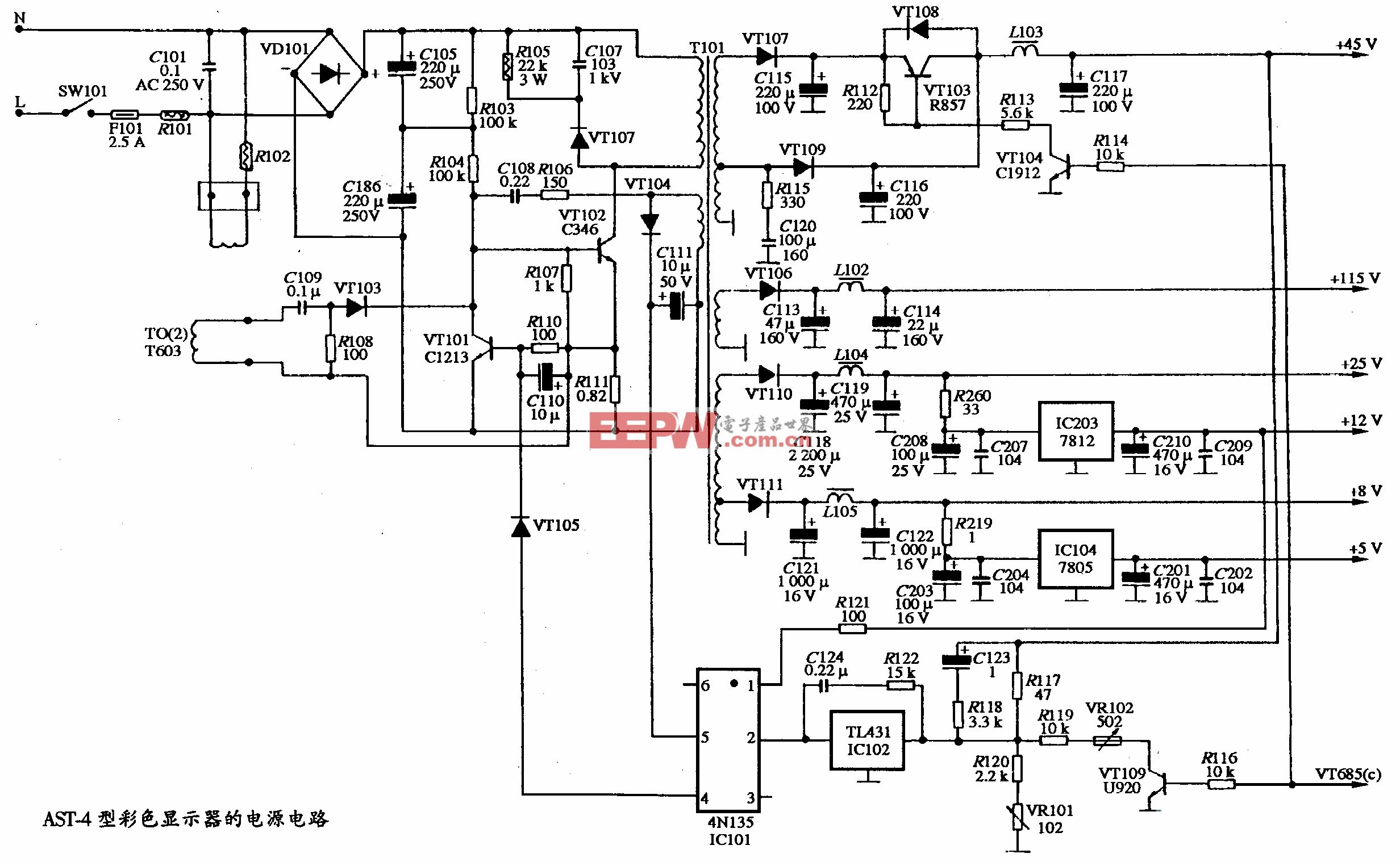

編碼系統以TMS320DM642高性能通用DSP芯片為核心。圖1為系統框圖。

圖1 編碼器系統框圖

1.1 TMS320DM642芯片的特點

DM642屬于TI公司的C64x系列DSPs。Veloci TI結構使C6000 DSPs在視頻和圖像處理中得到廣泛應用。CPU的VLIW結構由多個并行運行的執行單元組成,這些單元在單個周期內可執行多條指令。并行是C6000獲得高性能的關鍵。C64x在C6000的基礎上有一些重要的改進。除了有更高的時鐘頻率外,C64x從以前的Veloci TI結構擴展到Veloci TI.2結構,包含了許多新的指令,增加了額外的數據通道,寄存器的數量也增加了一倍。這些擴展使得CPU可以在一個時鐘周期內處理更多的數據,從而獲得更高的運算性能。

DM642芯片集成了各種片內外設,使得開發視頻和圖像領域的應用更為方便。它帶有三個可配置的視頻端口,提供與視頻輸入、視頻輸出以及碼流輸入的無縫接口。這些視頻端口支持許多格式的視頻輸入/輸出,包括BT.656、HDTV Y/C、RGB以及MPEG-2碼流的輸入。利用DM642開發視頻編碼器,其視頻輸入部分只需要一塊視頻采集芯片即可,如Phillips的SAA7113,無需外加邏輯控制電路和FIFO緩存,使硬件系統更為簡單和穩定。DM642的其它外設包括:10Mbps/100Mbps的以太網口(EMAC)、多通道音頻串口(McASP)、外部存儲器接口(EMIF)、主機接口(HPI)、多通道緩沖串口(McBSP)以及PCI接口等。

1.2 系統工作流程

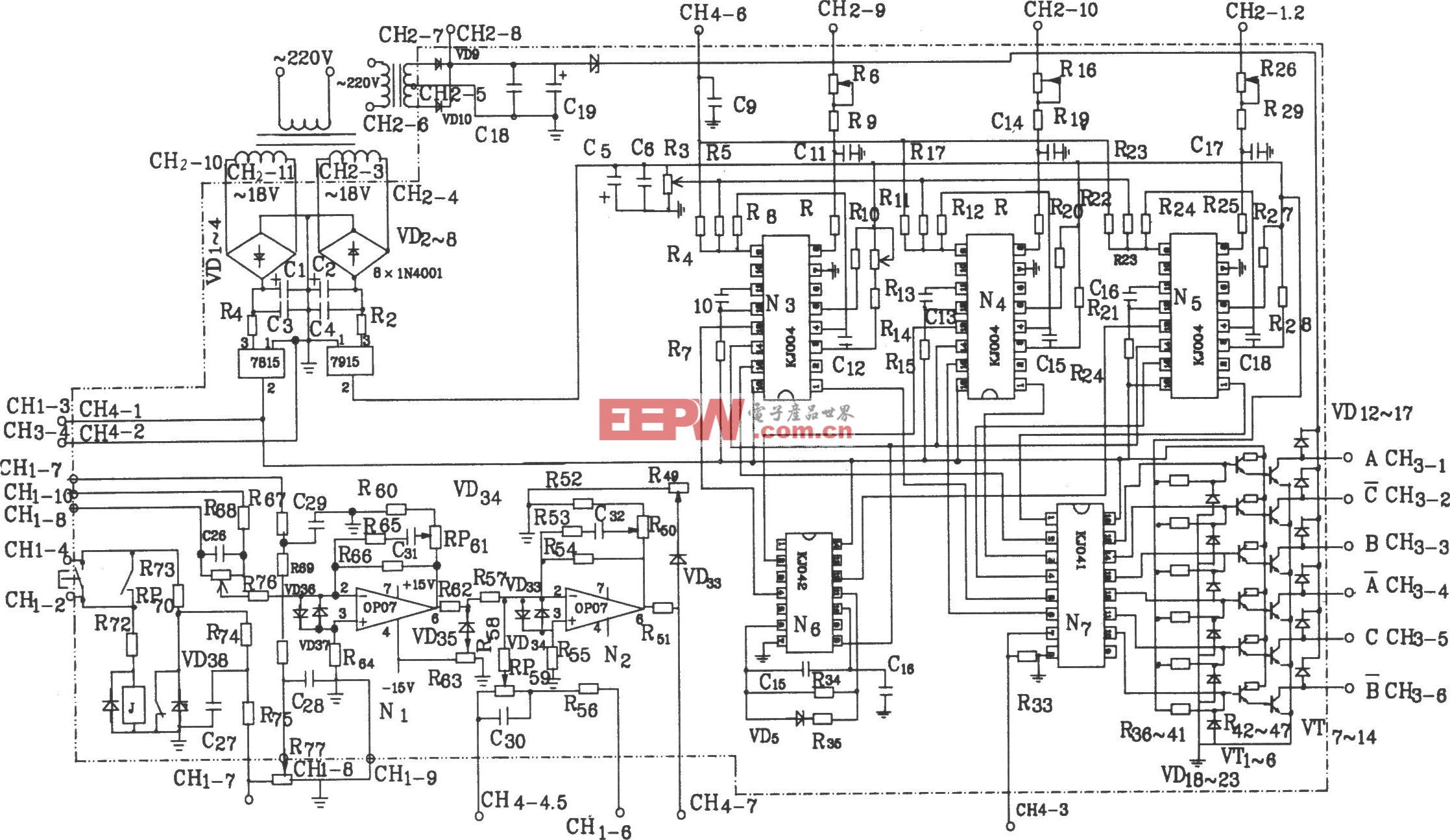

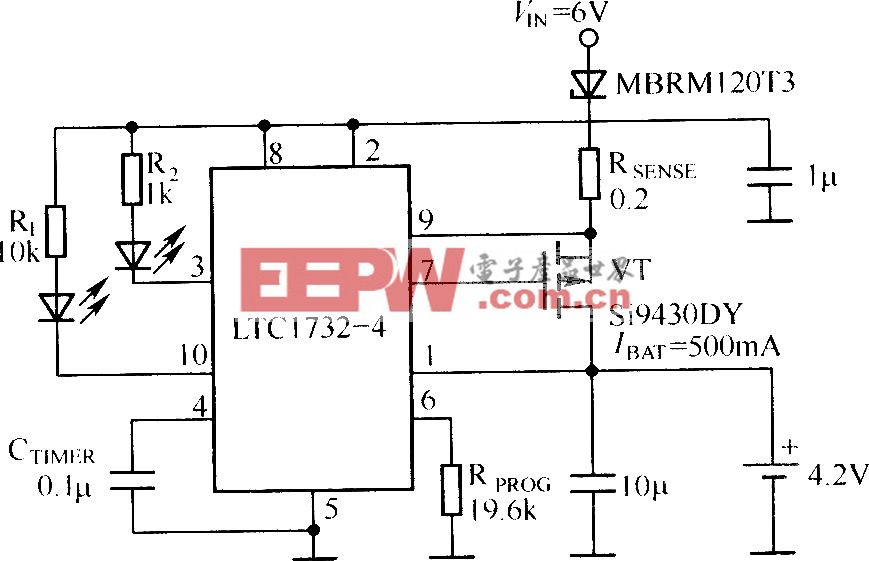

該編碼系統可分為圖像壓縮卡和主機兩部分。其工作流程如圖2所示。

圖2 系統工作流程圖

霍爾傳感器相關文章:霍爾傳感器工作原理

霍爾傳感器相關文章:霍爾傳感器原理

評論