PCI總線目標控制器的設計

0引言

PCI(PeripheralComponentInterconnect)總線是微型計算機中處理器/存儲器與外圍控制部件、擴展卡之間的互聯接口。PCI總線規范是互聯機構的協議,以及電氣和機械配置的規范,是當今高性能微型計算機事實上的總線標準。[1]

PCI總線控制器為PCI總線和用戶設備提供操作接口,協調PCI總線信號和用戶設備接口信號,使用戶設備能夠按照PCI總線的規范進行數據的傳輸。本文設計了一個適用于CMOS圖象處理的PCI目標控制器,具有較強的通用性。

1控制器的頂層設計

PCI總線目標設備在總線傳輸中處于被動地位,它不會申請對總線的使用權。當PCI總線上的某一主設備發起對本地資源的訪問時,整個控制邏輯的建立和數據傳輸的過程都是通過目標控制器實現的。

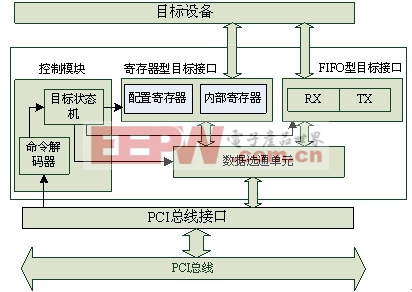

PCI系統中,目標設備在地址周期內響應總線主設備的傳輸要求,并配合主設備完成整個數據傳輸。圖1為目標控制器的詳細結構圖。

本設計將目標控制器按照功能分為幾個功能模塊實現,即命令解碼器、狀態機、FIFO類型目標接口和寄存器型目標接口。命令解碼模塊和狀態機構成目標控制器的控制部分,PCI主設備發起某類型的操作,目標控制器在地址周期內解析相應的地址和命令信息。在解析地址確定為本次操作的目標設備后,目標控制器會啟動目標設備狀態機根據當前解碼的信息進行一系列的控制操作。FIFO類型通道用于大批量的數據傳輸,可將本地存儲器塊掛接在該類型的數據通道上;寄存器類型接口用于數據量小的數據傳輸,該接口的后面可以掛接配置寄存器和一些本地功能設備的控制/狀態寄存器塊。這樣,PCI總線上的主設備既可以訪問到本地的存儲器設備也可以訪問本地的寄存器。下面從目標控制器的數據路徑和控制路徑分別進行論述。

2控制模塊實現

目標控制器的控制由兩部分完成,命令解碼器和目標狀態機。命令解碼器解碼來自PCI總線上的地址命令信息作為目標狀態機的輸入,狀態機鑒于此輸入執行相應的操作。

(1)命令解碼器:PCI總線主設備在地址周期內通過命令數據線(C/BE#)設置不同的編碼可以發起以下的操作,I/O讀寫、存儲器讀寫、配置讀寫、存儲器行讀/多行讀和存儲器寫及使無效。

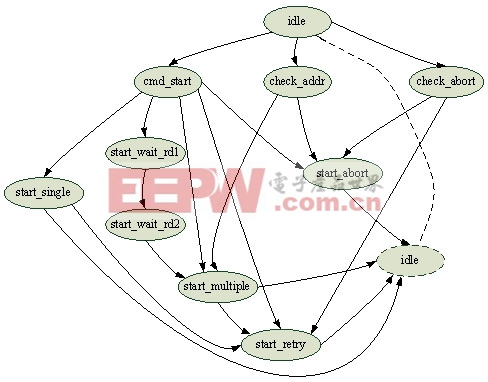

(2)目標狀態機[3]:對于PCI總線上傳來的信號,狀態機根據命令解碼器的解碼信息來控制總線控制器進行相應的操作。如果地址信息不正確或者本地的設備正忙于存取數據,狀態機會向PCI總線上發起本次操作的主設備回應目標丟棄或目標重試。目標狀態機的具體設計,如圖2所示。

評論