EPP高速數據采集與LabVIEW接口實現

可以實現PC機數據采集的接口很多,如ISA,PCI,EPP,USB等,其中最容易實現,而且性能很穩定的模式就是EPP模式。EPP指增強型并行接口標準(Enhanced Parallel Port),他電路實現簡單、時序穩定、與所有軟件接口容易實現、支持各種采樣速度,是用做數據采集比較理想的接口。

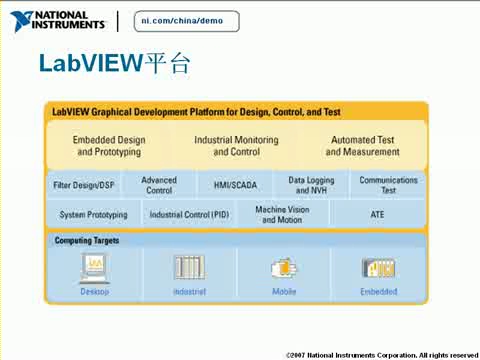

LabVIEW是現在應用廣泛的虛擬儀器開發軟件,他將數據采集與分析上的大多數方法都模塊化,以供用戶任意組合。其強大的圖形顯示能力及數據分析處理能力,不但降低了軟件開發難度,而且提高了用戶界面的可視性。

用LabVIEW驅動EPP接口進行數據采集,不但實現方法簡單,而且可以利用LabVIEW的顯示與分析工具,免去了買采集卡的昂貴費用和復雜的圖形界面程序編寫,具有經濟上和實現上的雙重優勢。

2 采集卡硬件電路設計

EPP模式實現了主機驅動的非對稱雙向數據傳輸,系統可獲得500 kB/s~2 MB/s的傳輸率。他是面向主機總線的,其所有的時序都由主機發出。首先,主機發出一個時序周期,然后把尋址地址發送到總線上,當主機產生地址選通信號時,地址就由外部電路鎖存。數據傳輸由數據選通信號進行。當被尋址器件應答一個準備好信號時,這個周期就被接收了[1]。

EPP提供了數據寫周期、數據讀周期、地址寫周期、地址讀周期4種數據傳送周期。圖1為常用的EPP握手硬件電路。每個讀寫周期都會按照圖1所示時序由硬件產生握手信號。其中握手信號nWait之前的2個非門是為了進行一定的延時,以保證數據讀周期內的正確性。

FIFO常用的是IDT720X系列。A/D轉換器應選用高速型。本設計選用的是IDT7203-35和Anal og公司的8位40 M的ADC9057840芯片。采樣電路如圖2所示。

評論