基于Actel反熔絲FPGA的高速DDR接口設計

1. 3 高速接口方案設計

本應用目標對FPGA 和DAC 之間的高速接口提出如下要求:

( a) DAC 輸出1 路115MHz 時鐘給FPGA;( b ) FPGA 輸出1 路115MHz 時鐘和2 路230Mbps 數據給每片DAC.

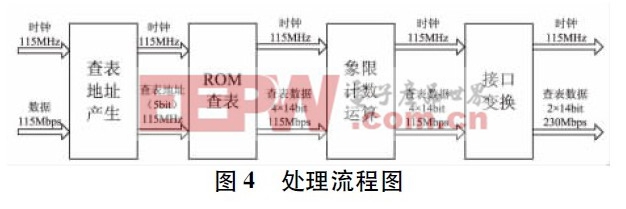

針對這一需求,考慮到FPGA 資源余量較大,為了降低系統運行速率,程序設計中遵循了用面積換取速度的原則,先采用115MHz 時鐘進行并行處理,產生4 路115Mbps 的14bit 量化數據,在輸出接口處將其轉換為2 路230Mbps 的14bit 量化數據,這樣可以使系統時鐘的速率降低一半。處理流程如圖4 所示。

輸出端接口變換部分是我們討論的重點,它對數據進行4 路到2 路的轉換,量化數據從115Mbps提高到230Mbps,有2 種方式可以實現:

方式一: 對輸入115MHz 時鐘進行2 倍頻得到230MHz 時鐘,使用異步FIFO 對數據進行4 路寫入,2 路讀出,寫鐘為115MHz,讀鐘為230MHz.

方式二: 將4 路14bit 的量化數據分為2 組,每一組均使用115MHz 時鐘進行DDR 輸出接口處理,從而使每一組的輸出均達到230MHz.

下面對2 種方式的可行性進行分析。

對于方式一,實現的關鍵在于2 倍頻時鐘的產生。按照手冊描述,Actel 公司AX 系列芯片作為反熔絲FPGA 中處理能力最強的器件,內部處理時鐘最高可以達到350MHz,且芯片內部集成了PLL( 延遲鎖相環) 資源,可以實現對數字時鐘信號的倍頻和分頻。而選擇RTAX-S 系列在AX 的基礎上進行了耐輻射能力加強,同時去掉了PLL 資源,原因是Actel公司通過實驗證明PLL 資源在空間環境中使用是不可靠的,這意味著倍頻無法在FPGA 內部實現。

因此,如果采用方式一,需要在FPGA 外部增加一個2 倍頻的器件,還要增加相應的電平匹配的電路,這一切對于230MHz 的數字時鐘信號實現上難度較大。

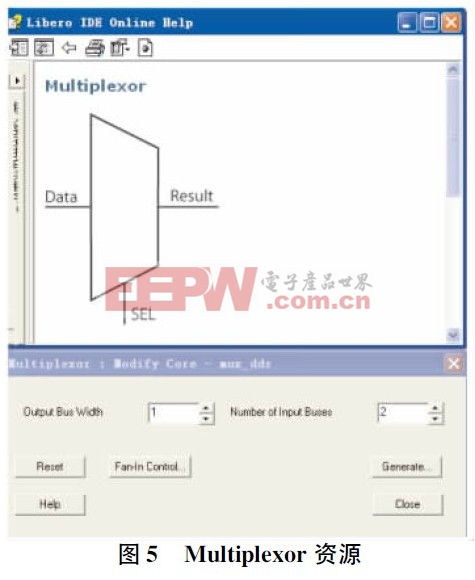

對于方式二,實現的關鍵在于DDR 輸出。通過查閱器件手冊可知,Actel 公司的RTAX – S 系列與Xilinx 公司SRAM 型FPGA 不同,其內部并沒有現成的DDR 輸出模塊可以調用,但是其內部有一種叫做Multiplexor 的多路選擇器資源,可以實現多路輸入到多路輸出的選擇控制,如圖5 所示。

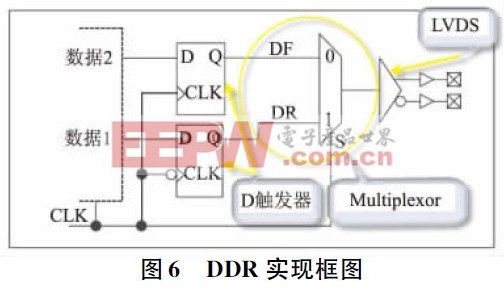

如果將其輸入Data 設置為2 路,輸出Result 設置為1 路,而時鐘作為控制信號SEL,則應當可以實現DDR 的效果。具體實現框圖如圖6 所示。

圖6 框圖實現的時序如圖7 所示,從圖7 可以看出兩路數據在DDR 變換后交替輸出,速率提高一倍,其中DR( 數據1) 先輸出,DF( 數據2) 后輸出。

評論