LVDS的接口電路設計

1 引 言

對于高速電路,尤其是高速數據總線,常用的器件一般有ECL、BTL和GTL等。這些器件的工藝成熟,應用也較為廣泛,但都存在一個共同的弱點,即功耗大。此外, 采用單端信號的BTL 和GTL器件,電磁輻射也較強。目前, NS公司率先推出的CMOS工藝的低電壓差分信號器件, 即LVDS給了人們另一種選擇。

2 LVDS技術簡介

LVDS(Low Voltage Differential Signaling)是一種小振幅差分信號技術,使用非常低的幅度信號(約350 mV)通過一對差分PCB走線或平衡電纜傳輸數據。它允許單個信道傳輸速率達到每秒數百兆比特,其特有的低振幅及恒流源模式驅動只產生極低的噪聲,消耗非常小的功率。

LVDS定義在2個國際標準中: IEEE P1596.3 (1996 年3 月通過) , 主要面向SC I ( ScalableCoherent Interface) ,定義了LVDS的電特性,還定義了SC I協議中包交換時的編碼; ANSI /EIA -644 (1995年11月通過) ,主要定義了LVDS的電特性,并建議了655 Mb / s的最大速率和1. 823Gb / s的無失真媒質上的理論極限速率。在2個標準中都指定了與物理媒質無關的特性,這保證了LVDS能成為多用途的接口標準。

3 LVDS器件的工作原理

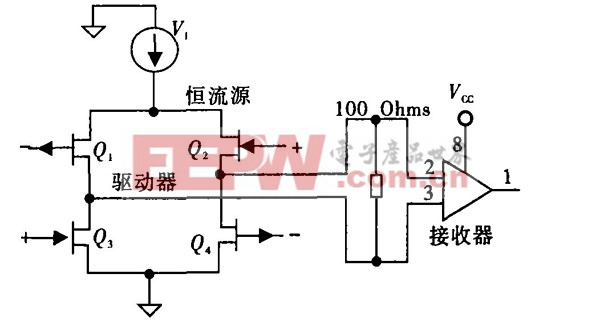

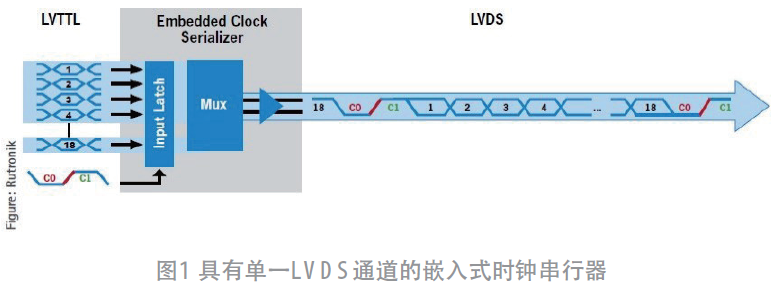

LVDS器件的工作原理如圖1所示。

圖1 LVDS的工作原理圖

LVDS驅動器由一個驅動差分線對的電流源組成,通常為3. 5 mA.LVDS接收器具有很高的輸入阻抗,因此驅動器輸出的電流大部分都流過100Ω的匹配電阻,并在接收器的輸入端產生大約350 mV的電壓。當驅動器翻轉時,它改變流經電阻的電流方向,產生有效的邏輯"1"和邏輯"0"狀態。

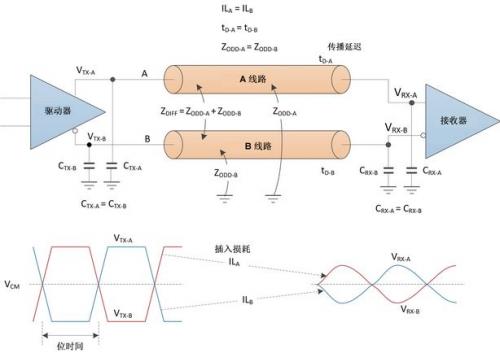

驅動器只有一個恒流源,這個差分驅動器采用奇模(Odd - mode)的傳輸方式,即等量的方向相反的電流分別在傳輸線路上傳送。電流會重新回流到雙絞線內,加上電流環路面積較小,因此產生最少電磁干擾。電源將供電加以限制,以免轉變時產生突變電流。由于并無突變電流出現,因此數據傳輸速度高達1. 5 Gb / s,但又不會大幅增加功耗。此外,恒流驅動器的輸出可以容許傳輸線路出現短路情況或接地,而且即使這樣也不會產生散熱上的問題。

差分接收器是一款高阻抗芯片,可以檢測小至20 mV的差分信號,然后將這些信號放大,以至達到標準邏輯電位。由于差分信號具有1. 2 V的典型驅動器補償電壓,而接收器可以接受由接地至2. 4 V的輸入電壓,因此可以抑制高達±1 V來自傳輸線路的共模噪聲。

由于邏輯狀態之間只有300 mV 的電壓差別,因此電壓變化極快, 但轉換速率不會加快。

又由于轉變速度減慢,使得輻射場的強度也大幅減弱。同樣,傳輸路線阻抗不連續性的反射也不會成為大問題,有助減低電波輻射量及信號的串擾。

4 LVDS與其他幾種邏輯電路的接口設計

由于LVDS是一種新技術, 因而在使用時LVDS和其他邏輯電路的接口設計就很重要,設計時,應注意以下幾個問題:

(1)根據系統的工作電源配置情況和需要傳輸的數據電平,合理選用驅動器和接收器芯片,或者根據接口芯片的情況,對被傳輸的數據首先進行電平轉換。

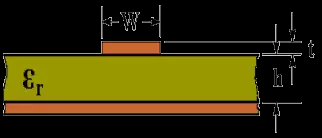

(2) 注意阻抗匹配。根據接收器輸入端的情況確定是否需要外接100 Ω 電阻,同時要根據PCB的板材和參數合理設計驅動器的線輸出阻抗,使其在90~107Ω 范圍內。PCB傳輸線要盡可能地短,因為過長的線路,不但傳輸衰耗加大,降低了傳輸速率,而且阻抗也容易失配,并可能影響到信號的完整性。

(3) 根據數據傳輸速率和傳輸電纜長度的關系,確定合適的電纜長度以滿足系統的要求。一般地采用LVDS方式傳輸數據,假定負載電阻為100Ω,當雙絞線長度為10 m時,傳輸速率可達400Mb / s;當電纜長度增加為20 m時,速率降為100Mb / s;而當電纜長度為100 m時,速率只能達到10Mb / s左右。

(4)多數LVDS接口芯片的使能端在片內沒有接上拉或下拉電阻。如果沒有驅動信號輸入,它們會不確定地被直接與地或VCC相連,有可能造成邏輯錯誤,所以除非有特別說明,接口芯片的使能輸入端不要懸空。

4. 1 LVDS之間的連接

由于LVDS的芯片內輸入端一般含有匹配阻抗,因此LVDS驅動器和LVDS接收器可以用一段連接線直接相連。

評論