多位接口提升串行閃存的性能

推動這類需求迅速增長的原因,要歸功于此類存儲器所具有的引腳數量少、板面積小、功率低和系統成本低等多方面優勢。采用8引腳標準SO封裝、標準串行外圍接口(SPI)的串行閃存比典型的32引腳封裝或更大的PLCC封裝并行閃存節省了約80%的板空間。

同樣重要的是,串行閃存大大降低了系統的設計復雜性。在MCU或ASIC之間,典型的32Mb并行閃存需包含21條地址線、16條數據線和3條控制線,而32Mb串行閃存只使用2條數據線和2條控制線。引腳數量較多的控制器要求使用較多的電路板布線層,控制器占用系統存儲器的引腳越多,可用來提供支持新特性所需要的處理能力和存儲器帶寬的引腳就越少。

為了滿足不斷增長的需求,Atmel、旺宏電子、Numonyx、Silicon Storage Technology (SST)、Spansion和華邦電子等串行閃存供應商已在提供更高密度的器件。Spansion公司去年發布了一款使用其90納米MirrorBit技術制造的128Mb SPI閃存芯片。但分析師表示,串行閃存想要切實進入新的應用系統,還將有賴于帶有多位接口的器件的出現。

串行閃存最初大多用在XiP(本地代碼執行)應用。為了直接從存儲器中執行這些程序,設計者使用可按單個字尋址的NOR閃存。但傳統的單個比特SPI接口的性能限制,迫使設計者在許多應用中結合使用基于SPI的串行閃存與影子RAM(通常是SRAM),以便支持更高的訪問速度。

|

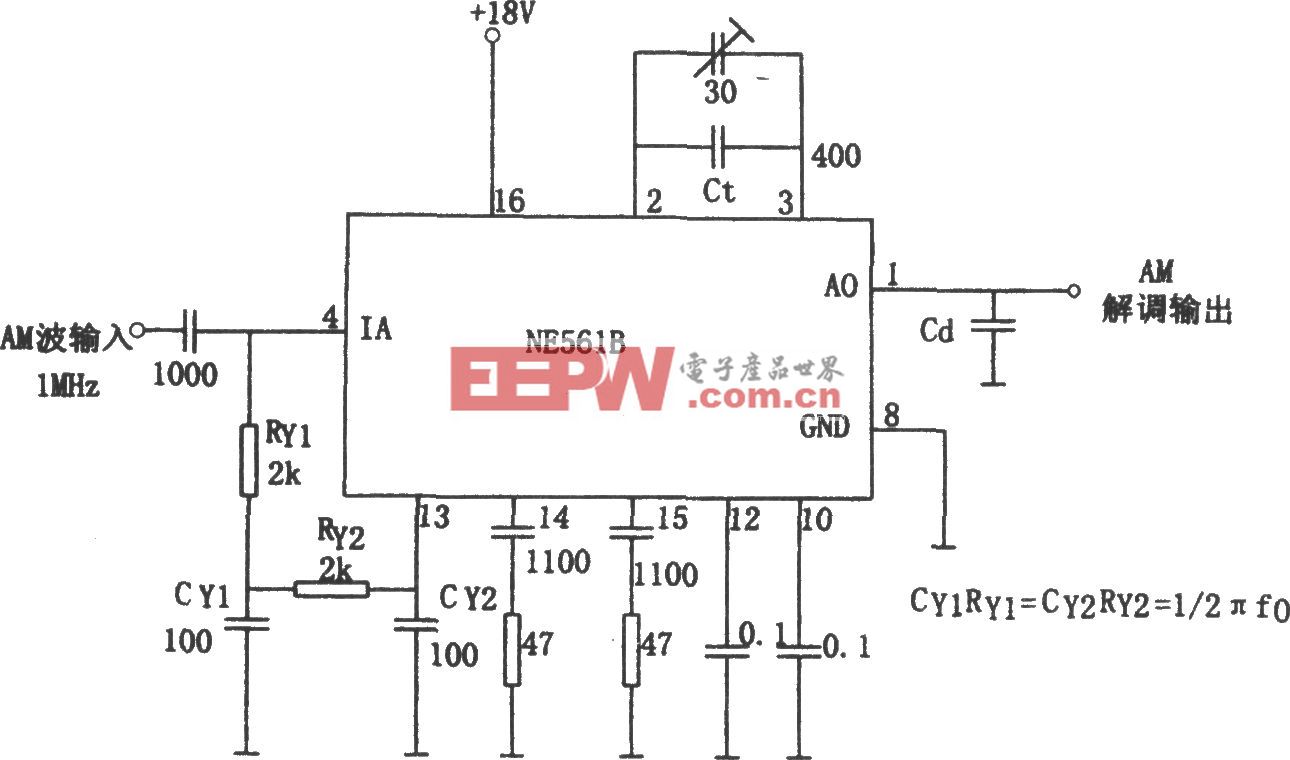

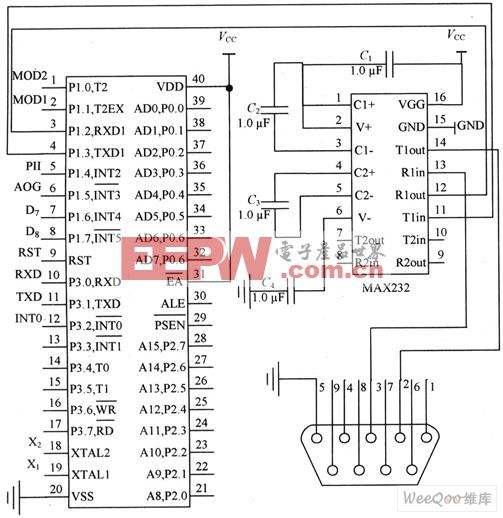

圖1:引腳數量少、占位小、功率低且系統成本低等優點推動了業界對串行閃存的需求。 |

為了克服這個限制、消除SRAM的成本并縮短啟動時間,已經有幾家制造商推出了帶有多位接口的器件。去年8月,華邦電子公司推出了據稱是全球首例的四通道SPI串行閃存芯片。這款16Mb存儲器采用了緊湊的8引腳SOP封裝,有單、雙和四通道I/O多種配置,是最大容量為64Mb的系列產品中的第一款。該器件最高時鐘速率為80MHz,四通道SPI模式的等效時鐘頻率最高為320MHz,這意味著其傳輸率是以50MHz頻率運行的標準串行閃存的6倍以上。由于每個讀指令所需要的時鐘數從40縮減到12,隨機訪問的開銷減少了70%。華邦電子公司聲稱,對于典型的32字節指令,四通道I/O器件的取指速率可達每秒32MB以上,與訪問時間為70ns和取指時間為100ns的同級別并行閃存相比,性能提高了50%。

旺宏電子公司也以雙通道I/O和四通道I/O器件把自己的產品線擴展到多I/O串行閃存。在傳統的串行閃存器件中,指令和數據通過串行輸入(SI)引腳寫入到存儲器。通過把串行輸入和串行輸出引腳從單一的單向數據流轉變成多個雙向流,旺宏電子公司的雙I/O器件把數據速率提高了一倍。該公司還把四I/O器件的寫入保護引腳(WP)和保留引腳(NC)改成雙向引腳,進一步擴展了這個概念。在四I/O模式中,據稱當數據或程序的代碼長度超過4個字節時,旺宏電子公司串行閃存的數據輸出速度超過了并行閃存。

傳統的單IO串行閃存在確定地址時需要使用40個時鐘周期,包括8個用于重寫讀指令的周期、24個用于地址分配的周期和8個啞周期。據報道,由于設法消除了在使用隨機尋址方式時指令尋址所需要的重復周期,旺宏電子公司的多I/O器件最多可節省20個時鐘周期。

最新問世的四I/O串行閃存來自SST公司。該公司的工程師們認為盡管現有的多位接口可以提高性能,但仍依賴于部分原始SPI架構(如笨拙的單比特指令結構、用于電源管理和預處理功能的外加指令)。SST公司開發了一個被稱為串行四接口(SQI)的架構,為了加快寫入和擦除的速度并改善低功率運行,該架構使用了一種可提升代碼執行靈活性的4位多路串行通訊協議。盡管該架構仍依賴于與SPI類似的串行指令來支持SPI協議(用于讀入、高速讀入和Jedec ID讀入),這些新功能還是可以支持高達350Mbps的持續增長的突發數據傳輸率。

不同于傳統的存儲器,SST公司的方法使用一種零延遲的半字節寬(nibblewide)架構,從而實現了真正的隨機訪問,該方法可以從任何地方開始讀入并可以跨越頁、塊或平面的界限而無需使用計數時鐘。該方法還依靠“環繞”特性(該特性使設計者能在無RAM應用中執行突發代碼片段、或當系統架構使用流水線技術傳輸時填充緩存行)支持8、16、32、64字節突發模式操作,縮短了訪問時間。該系統通過讀入存儲器索引的跳變(在256B的頁或64kB的塊之內從一個地址跳到另一個地址,或使用間接尋址方式從一個塊跳到另一個塊)減少了輸入時鐘的周期數。

評論