用OpenCV和Vivado HLS加速基于Zynq SoC的嵌入式視覺應用開發

用HLS加速OPENCV函數

本文引用地址:http://www.j9360.com/article/234277.htm一旦完成了嵌入式視覺系統架構的分區,找到了計算強度最大的部分,HLS工具就能幫助您加速這些函數,同時仍能繼續使用C++編寫。Vivado HLS用C、C++或SystemC代碼生成高效的RTL實現方案。

此外,以IP為中心的Vivado設計環境提供豐富的處理IP SmartCORE,能簡化到圖像傳感器、網絡及其它必要I/O接口的連接,簡化OpenCV庫中這些函數的實現。這相對于其它實現方案而言是一種明顯的優勢,因為其它方案哪怕是最基本的OpenCV I/O功能都需要加速。

為什么需要高層次綜合?

賽靈思推出的Vivado HLS是一款軟件編譯器,旨在將C、C++或SystemC編寫的算法轉變為針對用戶定義時鐘頻率和賽靈思產品系列器件優化的RTL。在C/C++程序解釋、分析和優化方面,它與x86處理器的編譯器具有相同的核心技術基礎。這種相似性有助于從臺式機開發環境快速移植到FPGA實現。您選擇目標時鐘頻率和器件后,無需用戶輸入,Vivado HLS會默認生成RTL實現。此外,Vivado HLS與其它任何編譯器一樣,也分不同的優化級別。由于算法最終執行目標是定制的微型架構,因此Vivado HLS可實現的優化級別比傳統的編譯器具有更精細的粒度。傳統的針對處理器的軟件設計O1 – O3優化理念被架構探索要求所取代,這些要求與用戶技術相結合,指導Vivado HLS創建盡可能出色的實現方案,滿足特定算法的功耗、面積占用和性能要求。

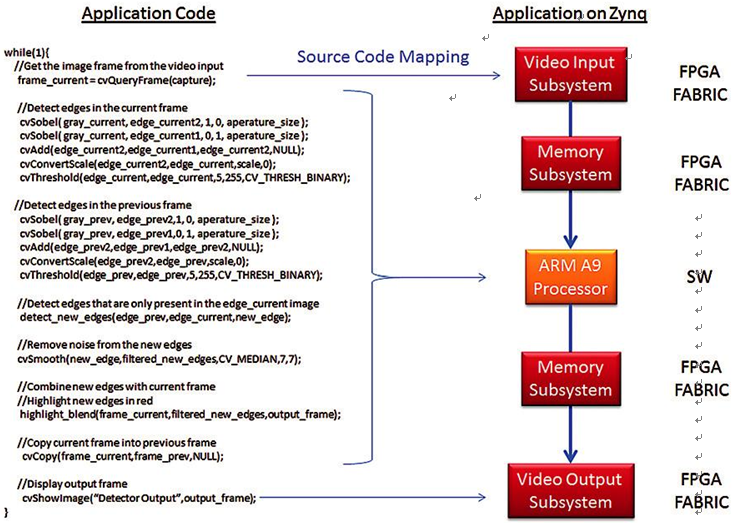

圖4 Zynq SoC上采用ARM處理器的運動檢測

圖2給出了HLS編譯器的用戶設計流程。從理念上講,用戶提供C/C++/SystemC算法描述,編譯器就能生成RTL實現。程序代碼轉化為RTL的過程分為四大階段:算法規范、微型架構探索、RTL實現和IP封裝。

算法規范階段是指將針對FPGA架構的軟件應用開發。該規范可在標準桌面軟件開發環境中,全面利用賽靈思提供的OpenCV等軟件庫進行開發。除了支持以軟件為中心的開發流程外,Vivado HLS還提升了從RTL到C/C++的提取驗證速度。用戶能用原軟件進行全面的算法功能驗證。通過Vivado HLS生成RTL后,生成的設計代碼類似于傳統軟件編譯器生成的處理器匯編代碼。用戶可在匯編代碼級進行調試,但這一步并不是必需的。

雖然Vivado HLS能處理幾乎所有針對其它軟件編譯器的C/C++代碼,但代碼有一個限制。在用Vivado HLS編譯代碼到FPGA過程中,用戶代碼不能包含任何運行時動態存儲器分配。與算法綁定于單個存儲器架構的處理器不同,FPGA實現采用特定算法的存儲器架構。通過分析陣列和變量的使用模式,Vivado HLS能確定哪些物理存儲器布局和存儲器類型最適合算法的存儲和帶寬要求。這種分析工作的唯一要求就是在C/C++代碼中明確描述算法使用的所有存儲器陣列。

從C/C++轉為優化的FPGA實現的第二步就是微型架構探索。在這一階段,您可運用Vivado HLS編譯器優化來測試不同的設計,以找到適當的面積和性能組合。您可在不同性能點實現相同的C/C++代碼,無需修改源代碼。Vivado HLS編譯器優化或要求規定了算法不同部分的性能如何描述。

c++相關文章:c++教程

評論