新型雙環900MHz、1800MHz頻段數字調諧系統

王仁發,林秩盛,陸南昌,熊 燕

(中山大學 電子與通信工程系, 廣州 510275)

摘 要:研究了DDS+雙PLL構成的新型數字調諧系統:A環產生DDS所需的時鐘信號,B環產生高頻輸出。B環使調諧器輸出頻率f0作較大變化,A環和DDS使f0作小變動。該系統工作頻率為850MHz~925MHz和1700MHz~1850MHz,頻率分辨率可達25kHz。在單片微機控制下,可實現跳頻。

關鍵詞:數字調諧系統 DDS PLL 跳頻

數字調諧系統是現代收發信機的核心,其性能直接影響通信質量的好壞,其主要部分是集成鎖相式頻率合成器。集成鎖相環與微處理器結合,可由微機控制完成頻率合成器的全部功能。

本文實現了一種與常規雙環方案完全不同的新雙環方案。該方案使用較高的鑒相頻率,采用直接數字合成(DDS)芯片,通過改變DDS的時鐘頻率和頻率控制字,使參考鑒相頻率產生較小的變化,就能改變環路的輸出頻率,達到精確頻率合成的目的。該方案既解決了小頻道間隔與高頻譜純度間的矛盾,又具有高的轉換速度;由單片微機完成計算和控制。

1 新方案原理

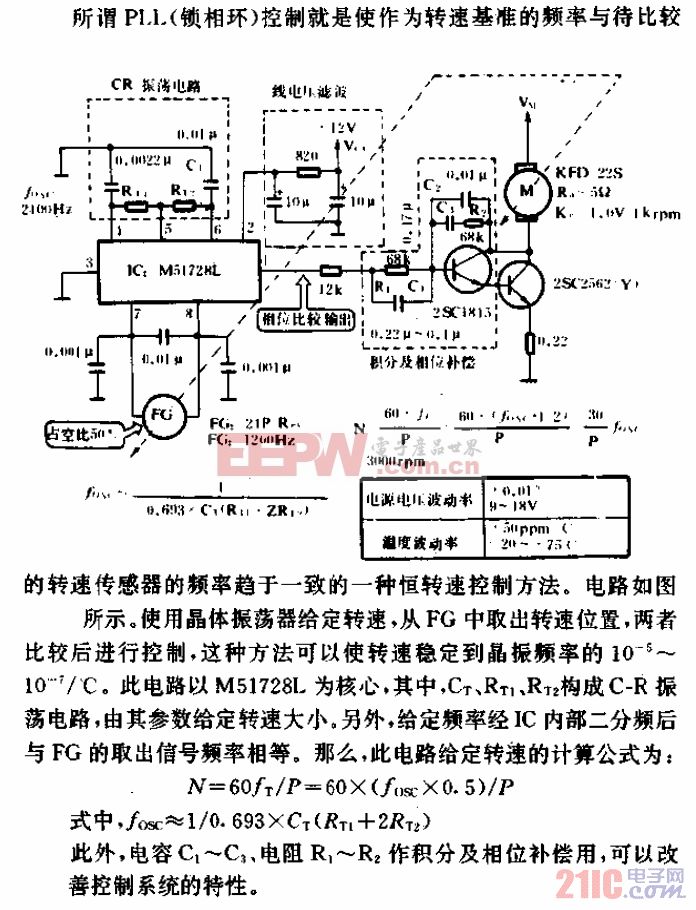

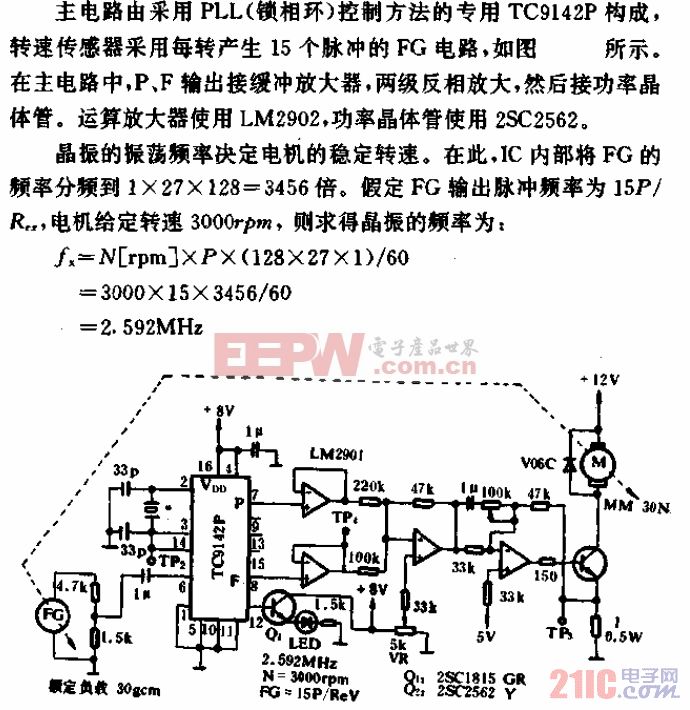

系統簡化原理圖如圖1所示。其中B環使調諧器輸出頻率f0作較大變化,A環為DDS芯片提供時鐘頻率fc,只要改變A環總分頻比NA和DDS的頻率控制字,使DDS輸出頻率fd作小變動,便可使f0以較小間隔頻率作步進改變。

圖1 方案原理圖

設A、B環中鑒相頻率分別為100kHz和300kHz(由晶振與fd分別經參考分頻器得到),雙模分頻與頻率合成芯片中的程序分頻的總分頻比分別為NA和NB,f0=1700MHz~1850MHz,f´0=850MHz~925MHz,△f0=25kHz,則由環路鎖定時的頻率關系得到△fd=4.16Hz~4.41Hz;所以只要△fd≤4.41Hz,便可使輸出的頻率分辨率達到25kHz。一般DDS的輸出頻率間隔做到小于0.1Hz,即可滿足本要求。同理,當△f0=

評論