基于MPC8260處理器和FPGA的DMA接口設計

引言

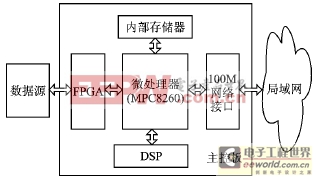

在基于軟件無線電的某無線通信信號偵收平臺的設計中,天線接收到的信號經過變頻器處理和A/D變換之后,經過高速通道把采集的信號送入主控板進行數據分發處理。系統的結構框圖如圖1所示。

圖1 主控板的系統結構框圖

主控板的硬件核心是嵌入式微處理器MPC8260,負責系統軟件的加載、數據的分發以及與外界命令控制的交互。軟件上,采用高性能的VxWorks嵌入式實時操作系統。從天線接收到的射頻信號經過變頻和A/D變換之后作為數據源連接到FPGA,FPGA對接收到的數據進行中頻變換和信道估計等預處理后,在CPU的控制下將數據傳輸到本地內存,最后CPU對數據打包后進行快速分發。因此,將40~50 Mbps的高速數據流從FPGA傳給CPU成為系統設計的一個關鍵。

如果每傳遞一個字節的數據都需要CPU的介入,那么不論是采用中斷驅動還是采用程序查詢的方式,數據傳輸速率都會很低,無法滿足系統需求。DMA(直接存儲器存取)和一般的程序控制傳送方式相比具有數據傳送速度高、I/O響應時間短和CPU額外開銷小的優點,因此,選擇DMA的傳輸模式,使FPGA中的數據不經過CPU內部寄存器的中轉而直接存放到本地內存。MPC8260支持多種DMA實現方式,分別適用于不同數據傳輸源/目的設備、不同傳輸數據塊大小和存儲模式的需要,因此需要根據主控板的系統特點設計出合適的DMA傳輸接口。

1 MPC8260的 DMA系統結構

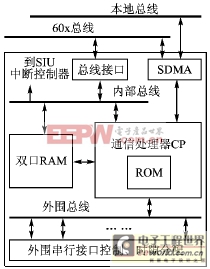

圖2 CPM原理框圖

MPC8260是Freescale公司主要針對數據通信領域而設計的一種嵌入式

圖2中, CPM內除了SDMA模塊以外,還包括通信控制器(Communications Processor,CP)、雙口RAM和一些串行外圍設備的控制接口等。SDMA和60x總線、本地總線相連,并且可以直接訪問CPM內部的雙口RAM。CP利用這兩個SDMA為每個外圍串行控制器提供了兩個虛擬SDMA通道:一個用于輸入,一個用于輸出。同時,CPM還用這2個物理的SDMA通道

主控板上的FPGA和SDRAM都是掛接在MPC8260的60x總線上的,所以只能利用IDMA來實現二者之間的DMA傳輸。根據傳輸啟動的觸發方式不同,IDMA可分為握手信號控制的IDMA傳輸和CP命令控制的IDMA傳輸兩種。下面分別介紹兩種方式的特點。

1.1 握手信號控制的IDMA傳輸

握手信號控制的IDMA傳輸主要用于外設和內存之間的數據傳輸。每個IDMA通道都有3個握手信號用于傳輸握手控制:DMA請求信號DREQ[1~4]、DMA應答信號DACK[1~4]和DMA結束信號DONE[1~4]。

在這種方式下,PowerPC內核只需要參與IDMA通道初始化,之后的傳輸過程全部由CP按照通道參數設置和握手信號控制數據的收發,在最大程度上釋放內核。握手信號控制的缺點在于:① SDRAM中的數據和MPC8260的數據同步比較復雜。② 每次發出請求信號后都要進行總線仲裁,并且在得到總線使用權之后一次只能夠傳輸外設端口大小或者32位的數據,總線利用率低。③ 握手控制邏輯和時序比較復雜,加重了FPGA內部控制邏輯設計的負擔。

雖然這種傳輸方式基本上不占用內核資源,但是由于總線帶寬有限且利用率較低,所以在連續高速的通信條件下會造成內核長時間得不到總線使用權而一直處于等待狀態。因此,握手信號控制的IDMA一般只適用于由外設發起的、數據不是太頻繁的傳輸使用。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論