約束設置與邏輯綜合在SoC設計中的應用

摘 要: 介紹了約束設置與邏輯綜合在SoC設計中的應用,并以一款SoC芯片ZSU32的設計為例,詳細討論了系統芯片的約束設置與邏輯綜合策略。

系統芯片SoC是目前超大規模集成電路設計的發展趨勢,其集成度高、功能復雜、時序要求嚴格。邏輯綜合是SoC設計不可缺少的一環,它是將抽象的以硬件描述語言所構造的模型轉化為具體的門級電路網表的過程。邏輯綜合的質量直接影響芯片所能達到的性能,因而在綜合過程中必須根據設計要求在時序、面積和功耗方面設置正確的約束。

本文針對中山大學ASIC設計中心自主開發的一款系統芯片ZSU32,以Synopsys公司的Design Compiler為綜合工具,探索了對SoC芯片進行綜合的設計流程和方法,特別對綜合過程的時序約束進行了詳細討論,提出了有效的綜合約束設置方案。

1 時序約束原理

同步電路是大多數集成電路系統的主流選擇。同步電路具有工作特性簡單、步調明確、抗干擾能力強等特點。但是,因為所有的時序元件受控于一個特定的時鐘,所以數據的傳播必須滿足一定的約束以便能夠保持與時鐘信號步調一致。

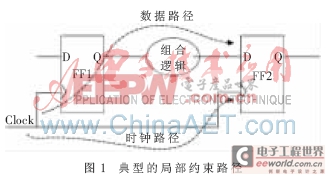

圖1是一個典型的局部路徑,它需要滿足兩方面的條件:防止數據太遲到達目的寄存器導致數據不能正確保存;防止新的數據過早到達導致覆蓋了前一數據。

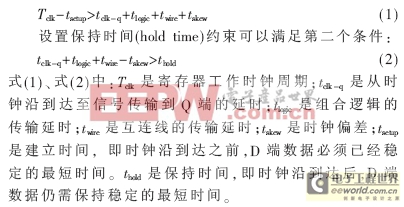

設置建立時間(setup time)約束可以滿足第一個條件:

評論