Stratix系列FPGA電源方案設計分析

兩個PWM控制器都使用低端MOSFET導通電阻(RDS(ON))進行電流監控。檢測到的電壓降與OCSETx腳和地之間的電阻(如圖3中R8、R9)設置的門限相比較:

ROCSET=

其中,IOC是規定的過流保護門限,RCS是與ISENx腳相連的電流感應電阻。如果過流持續2個時鐘周期,則進入Hiccup模式,門驅動器斷開,進入軟啟動。重新啟動前,IC在軟啟動過程中要循環兩次。IC會在軟啟動過程中持續循環,直到過流現象消除為止。

圖3中SYNC腳用來實現兩個或多個ISL6443控制器的同步。使用時需接下拉電阻,不用時將其與VCC_5V相連。

2.2 PCB布局考慮

布局對基于ISL6443的DC-DC轉換器的成功實現非常關鍵。ISL6443工作在高頻模式下,開關時間非常短,在這種開關頻率下,即使最短的連線也會產生較大的阻抗。同時,峰值門驅動電流也會在極短的時間內顯著升高。電流從一個器件到另一器件的轉換速度引起互連阻抗和寄生電路元件上的電壓尖脈沖。該電壓尖脈沖會降低效率,產生EMI,增加過壓應力和阻尼振蕩。仔細考慮PCB板布局,可使電壓尖脈沖的值最小。針對以上考慮總結了幾點布局上需注意的地方[4]:

(1)輸入電容、高端FET、低端FET、電感和輸出電容應首先放置。將輸入高頻去耦電容放在非常靠近MOSFET的地方。

(2)在IC附近建立一個小的模擬接地平面。將SGND腳接至該平面,包括反饋電阻、電流極限設置電阻以及SDx下拉電阻的所有小信號接地端都接至SGND平面。

(3)高電流接地端PGND與小信號接地端SGND必須分開,在靠近IC的地方將SGND和PGND相連。

(4)確保從輸入電容到MOSFET、輸出電感和輸出電容的電流通路盡可能短,同時有最大的容許線寬。

(5)將PWM控制器靠近低端FET 放置。LGATE 的連接應該較短而且較寬。IC最好放置在無噪聲接地的地方。

(6)將VCC_5V旁路電容接在非常靠近VCC_5V腳的地方,將它的接地端接至PGND上。將門驅動元件自舉二極管和自舉電容放在接近IC的地方。

(7)輸出電容應盡量靠近負載。用短而寬的覆銅層連接輸出電容和負載,避免產生感抗和阻抗。

3 實驗數據分析與驗證

利用Catena公司提供的SIMetrix/SIMPLIS仿真工具實現了該電源方案的分析和驗證,具體方法可查閱參考文獻[6][7][8]。

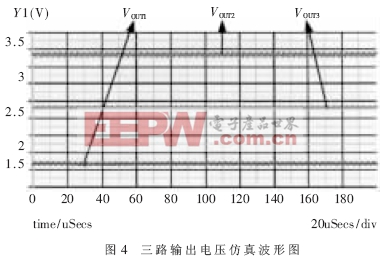

圖4所示為ISL6443三路輸出電壓波形,PWM控制器門驅動器的電壓上升和下降時間均為18ns左右。因此,三路輸出電壓能在極短的時間內達到穩定值,從而滿足了FPGA的性能要求。

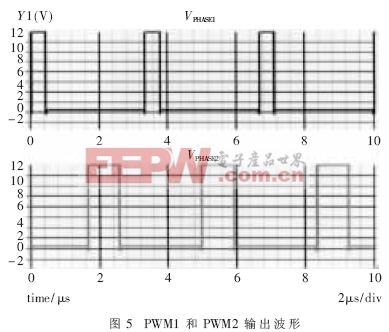

圖5所示為兩個PWM控制器的輸出波形。圖中可以看出,ISL6443的兩個PWM控制器呈180°異相工作,以減小輸入紋波電流。這降低了對輸入電容紋波電流的要求,減小了電源的感生噪聲,同時也提高了EMI抗干擾性能。

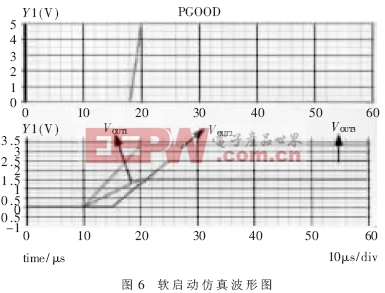

圖6所示為ISL6443軟啟動仿真波形。軟啟動功能使轉換器的輸出被監控,得到過載、短路和欠壓保護。輸出持續過載會使PGOOD置低,從而進入軟啟動模式,直到過載現象消除為止。

本文利用Intersil高效三輸出同步補償穩定器實現了StratixTM FPGA的電源系統設計,并且進行了一系列的仿真分析與驗證實驗。實驗表明該設計方案合理有效,易于實現,有較好的參考價值和實用價值。

評論