基于CoolRunner CPLD的MP3應用開發板的設計

MP3應用開發板的選型和設計

主控模塊芯片及其外圍器件

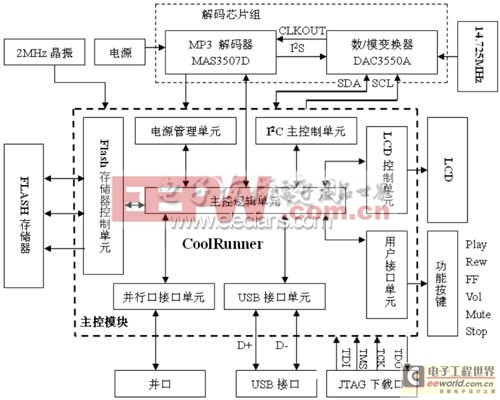

XCR3256是Xilinx公司開發的CoolRuner CPLD芯片,可實現6000門的數字邏輯電路,內嵌256個宏單元,支持4個全局時鐘,具有低功耗、可快速ISP、延時可預測等特點,可滿足MP3功能和數碼產品方面的一些特殊要求,我們選用XCR3256芯片實現M P3主控模塊。該主控模塊用于對各外圍器件的控制,協調各外圍器件的工作。外圍器件主要有解碼芯片組(MAS3507D和DAC3550A)、Flash存儲器、LCD、USB接口、并口等。主控模塊與各外圍器件的框圖如圖1所示。

圖1 MP3應用開發板結構框圖

主控邏輯單元是整個主控模塊的核心部分,決定著MP3播放器各功能,如播放、快進、下載之間的優先度和順序,為其他邏輯單元提供實現更加復雜操作的控制信號。主控邏輯單元通過狀態機對其他模塊進行控制,其狀態機如圖2所示,該圖詳細地描述了MP3播放器不同工作階段的操作條件和各階段之間的切換情況。

特別需要說明的是:①LOW_PWR使DAC3550A工作在低功率模式下;②IDLE是播放與下載、快進、后退等操作之間的轉換狀態;③UPDATE_TRACK將歌曲曲目更新,并傳遞給LCD顯示。

圖2 主控邏輯單元狀態機

DAC3550A是一款專為音頻應用而設計的高精度數模轉換芯片,具有低功耗操作模式,連續采樣頻率從8KHz到50KHz均可自主選擇,這就給設計帶來了極大的靈活性;還提供了簡潔的I2S總線接口和I2C總線接口,主控模塊正是通過I2C總線對DAC3550A三個寄存器AVOL(16bits)、GCFG(8bits)、SR_REG(8bits)寫入相應命令而實現控制的。DAC3550A接口電路圖設計如圖3所示。

圖3 DAC3550A接口電路圖

評論