基于FPGA的數據采集及顯示

摘 要: 在電力系統諧波分析中,模數轉換(ADC)電路是影響系統檢測性能的主要環節之一。基于NiosII的諧波分析系統具有邏輯控制能力強、信號處理實時性高、系統抗干擾能力強等特點。以Altera公司的DE2開發板為平臺,實現了采樣電路的硬件設計;在Quartus II 中用Verilog HDL語言完成了與FPGA的接口設計,并最終實現VGA顯示。

關鍵詞: ADC;NiosII;FPGA;諧波分析;VGA

諧波是電力系統的一大公害,消除諧波污染,把諧波含量控制在允許范圍內,已經成為主管部門和用電單位的共同奮斗目標。而要消除電網中的諧波,首先就要對諧波進行準確測量,諧波測量工作已經越來越引起人們的關注[1]。A/D轉換電路是電力系統諧波測量中必不可少的一個重要環節,是電力系統諧波測量系統前端的核心。

FPGA因具有強大的邏輯控制能力、高速的運算能力、靈活的可編程性,已經越來越多的被用于各種數字系統。在FPGA內部一般都內嵌有可配置的高速RAM、PLL、LVDS、LVTTL以及硬件乘法累加器等DSP模塊。用FPGA模塊來實現數字信號處理可以很好地解決并行和順序性的矛盾,直至速度問題,而且其靈活的可配置性,使得FPGA構成的DSP系統非常易于修改,易于測試及硬件升級。在QuartusII開發軟件中用Verilog HDL硬件描述語言能夠很容易進行邏輯電路設計,并且在FPGA中可以實現用硬件進行配置,可有效降低軟件運行時間和軟件設計復雜程度[2]。因此,FPGA非常適合在電力系統諧波測量系統中作為核心器件。

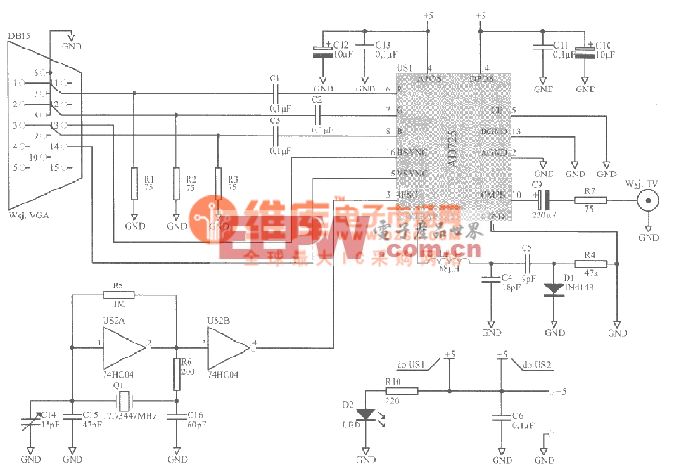

本文中采樣電路選用AD73360,在QuartusII中用Verilog HDL硬件描述語言實現了AD73360及VGA與FPGA的接口設計,最后通過實驗驗證了設計的正確性。

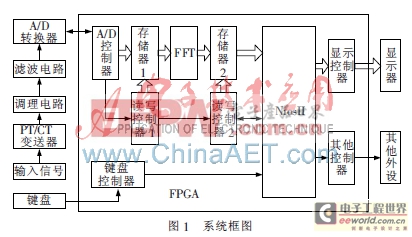

1 系統總體方案

系統以Altera公司的DE2開發板為平臺,系統框圖如圖1所示。信號采集單元核心器件為電壓、電流互感器。互感器將待測高壓、大電流信號線性轉換為合適的微弱電壓信號,該微弱電壓信號經信號調理電路放大為合適的電壓信號,經低通濾波電路濾除高于2 500 Hz的高頻噪聲,然后送到A/D轉換單元進行A/D轉換,轉換后形成數字信號存儲到存儲器中,再送到FFT處理單元進行快速傅里葉變換,變換后得到的數據再儲存到存儲器中,再進行一系列相關運算,如:諧波電壓含有量、諧波電流含有量、各次諧波電壓含有率、各次諧波電流含有率等,最后經VGA進行顯示出波形和相關數據。

2 AD73360的配置[3]

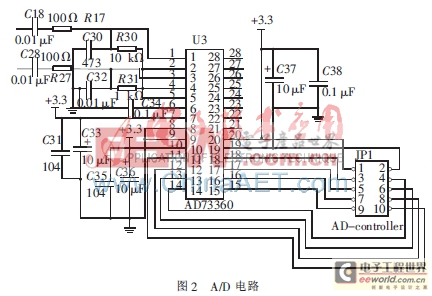

2.1 A/D電路設計

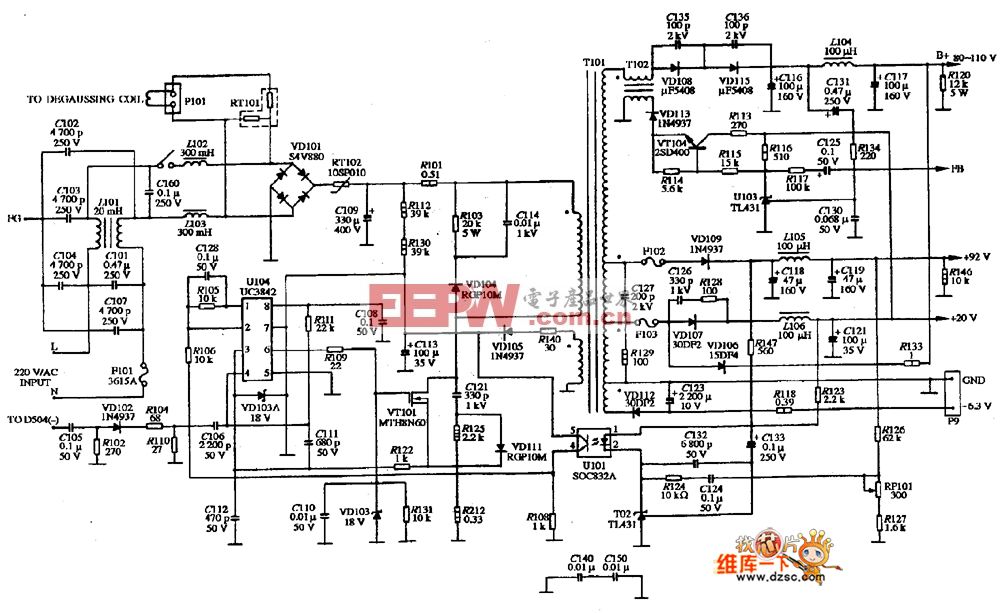

A/D電路如圖2所示。A/D電路可分為以下三個部分。

(1)電源部分。AD73360有5 V和3 V兩種工作模式,為了能夠與FPGA實現直接連接,采用3 V供電(FPGA接口電平為3.3 V左右),這樣無需外加電平轉換電路,可以簡化電路設計、降低系統功耗、節約成本。

(2)模擬輸入部分。AD73360有6個通道,每個通道又分為正端VINP和負端VINN,每個通道都可以由AD73360內部控制寄存器配置為差分輸入和單端輸入兩種方式,本設計采用單端交流耦合輸入方式。

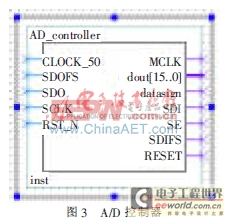

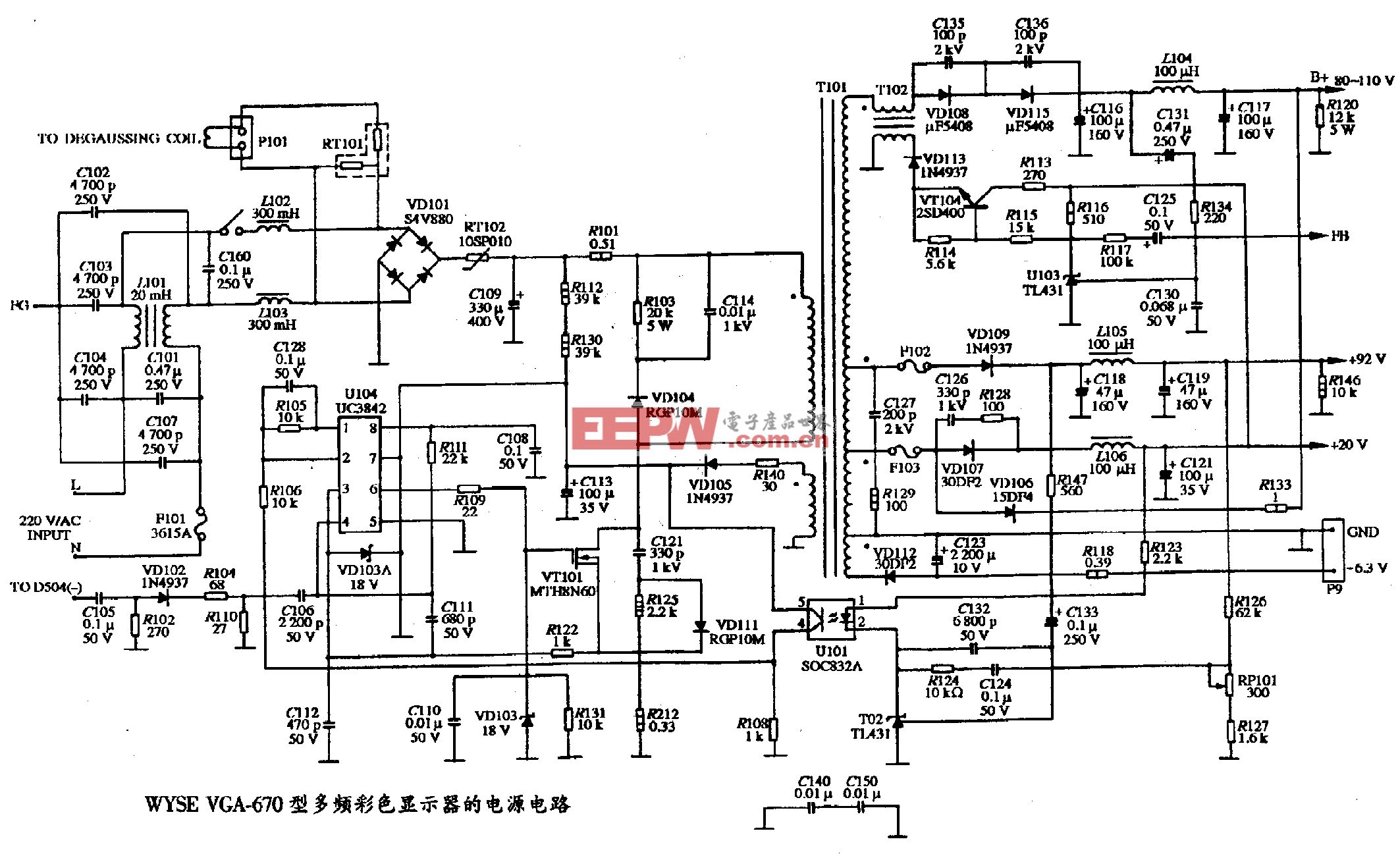

(3)與FPGA接口部分。AD73360采用六線制串行接口,能很方便與外部電路實現接口連接,為了實現AD73360與FPGA的連接,就需要在FPGA中設計一個控制器,在Quartus II中設計的A/D控制器AD_controller如圖3所示。

2.2 AD73360的配置

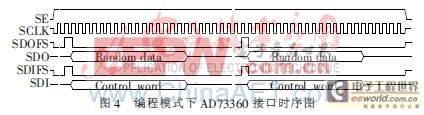

AD73360為可編程A/D轉換器,每次啟動系統都要對其進行配置。對AD73360的配置有兩種方式,一種方法是用程序來實現,另外一種方法是利用FPGA具有很強的邏輯控制能力,用硬件實現對AD73360的配置,后者雖然會占用一些硬件資源,但是這樣可以大大簡化系統程序設計,節約軟件運行時間,因此本設計采用后者。系統上電或者手動復位后,AD73360被復位,在復位狀態下,AD73360的八個控制字寄存器被初始化為00H,同時AD_controller也被復位到初始狀態,SE被置1,從而AD73360串口進入工作狀態。當復位信號變為高時,AD73360進入編程模式,該模式下,AD73360數字端接口時序如圖4所示。在編程模式下,AD73360的SDOFS引腳以主時鐘頻率的1/2048的頻率產生輸出數據標志信號,當控制寄存器被正確配置后,將產生與設定采樣頻率同頻的SDOFS標志信號,每個輸出標志信號以后SDO引腳將連續輸出16位隨機數據,這時候的數據是隨機產生的,不是有效的A/D轉換數據。與此同時,在SCLK時鐘的下降沿,若SDIFS標志位有效,則AD73360于下一個SCLK下降沿開始讀取SDI引腳數據,并存到AD73360中的串行寄存器。

撤銷復位信號后,AD_controller開始對AD73360進行配置,配置過程如圖4所示。系統復位后標志信號GO被置1,經過三個SCLK時鐘周期后GO被置0,此時把第一個配置數據賦給SD,標志信號GO保持一個SCLK時鐘周期后,又被置1。當標志信號GO=0時,AD_controller進入下一狀態檢測SDOFS,當檢測到SDOFS由1變為0時,進入寫數據狀態,從SD最高位開始由高到低逐位往SDI端口寫數據,每個SCLK時鐘周期寫一位,直到寫完16位數據,AD73360根據這16位數據的前8位數據針對把后8位數據寫入相應AD73360的相應控制寄存器,寫完16位數據后,系統把SDIFS引腳設為高阻狀態,并產生一個SCLK周期的END(對END置1)信號,作為一個控制字配置完成的標志。系統檢測到END標志信號后,在未對所有控制字進行有效配置的情況下,把下一個控制字賦給PDATA,并產生一個SCLK周期的GO(把GO置0)標志信號,系統檢測到GO標志信號后,再檢測SDOFS,在SDOFS為1的下一個SCLK開始通過SDI端口向AD73360寫下一個控制字,直到8個控制字都被寫入AD73360,配置完成后,AD73360進入數據模式,開始進行A/D轉換。完成配置任務后AD_controller結束配置狀態,把SDI設為高阻狀態,并開始接收SDO引腳的數據,并把接收到的串行數據轉換成16位并行數據[4]。

在QuartusII開發工具中,用Verilog HDL語言完成了對AD73360的配置,并進行了功能仿真,功能仿真結果如圖5所示。

評論