基于FPGA的大屏幕全彩LED掃描控制器設計

1 引言

作為大型平板顯示設備的一種,LED 顯示屏以其使用壽命長、維護費用低、功耗低等特點在顯示領域占有重要的位置。特別在近年,帶有紅、綠、藍三基色以及灰度顯示效果的全彩LED 顯示屏,以其豐富多彩的顯示效果而倍受業界關注,成為LED 顯示屏市場近年增長幅度比較大的產品。壽命、單位面積亮度、三基色的偏差程度、點距、對比度、灰度等級(包括灰度級數和線性度) 、掃描頻率等指標性能是衡量或橫向比較大型顯示設備好壞的標準。而這些指標性能的優劣,很大程度上決定于掃描控制器的性能。因此對大屏幕全彩L ED 顯示掃描控制方法的研究有著重要的意義。

由于LED 的發光亮度與掃描周期內的發光時間近似成正比,所以灰度等級的實現通常是由控制LED 的發光時間與掃描周期的比值,即采用調節占空比來實現的。全彩LED 顯示屏一般采用逐位點亮的掃描方式實現灰度圖像顯示。對于顯示灰度級數為8 位的LED 顯示屏,一般采用“19場掃描”原理來實現256 級灰度顯示。L ED顯示屏的顯示數據更新一般采用串行輸出方式,如采用595 進行設計的靜態LED 全彩顯示屏,根據“19 場掃描”原理,對于分辨率等規格確定的屏體,當串行移位時鐘確定時,顯示屏的刷新頻率和LED 的發光效率(一個掃描周期內,LED的最長點亮時間所占的比例) 也就被確定。本文提出了一種新的逐位點亮掃描方式,該方式對典型的“19場掃描”方式進行了改進,可以在串行移位時鐘確定的條件下,在一定范圍內對刷新率和發光效率進行調節,從而提高了產品根據實際的應用環境和客戶要求進行設計的靈活性。

2 逐位點亮的灰度實現算法設計

以8 位“19場掃描”理論為例,所謂逐位點亮,即從一個字節數據中依次從低位到高位或者從高位到低位提取出一位數據,分8 次點亮對應的像素,每一位對應的點亮時間與關斷時間的占空比不同。如果點亮時間從低位到高位依次倍增,則合成的點亮時間將會有256 種組合。定義D0 位對應的點亮時間加上關斷時間為一個時間單位,設為T ,可得表1 所示各位的點亮與關斷時間。

表1 “19場掃描”顯示時各位的點亮與關斷時間

在實際設計中, T也是對LED 顯示屏進行一次串行數據更新所需要的時間。表1 所示的總時間是T 的整數倍,所以每個數據位所占用的總時間可以通過刷新一次屏幕數據來進行定時。在進行LED顯示屏設計時,整個顯示屏中LED 的亮與滅可以通過總控線EN 控制,當點亮時間≥1 T時,EN 控制顯示屏處于常亮狀態,而當點亮時間 1 T 時,可以通過控制EN 產生相應占空比的控制波形來實現相應位的亮度控制。可見,利用“19場掃描”原理,在串行移位時鐘和屏體具體規格確定的情況下,其刷新率也就被確定了,并且具有固定的發光效率η。

η =6 點亮時間6 總時間≈ 16 T19 T≈ 84 % (1)由灰度顯示的原理可以知道,能否實現灰度顯示,決定于各個數據位的點亮時間從低位到高位是否以2 的倍數遞增,而關斷時間的長短只會影響發光效率的大小。在進行系統設計時,使用了8~10 位的非線性灰度校正,因此需要實現10位灰度掃描控制。定義“t”為點亮時間的一個時間單位,則可得表2 所示的時間分配。如果定義數據為“1”有效(點亮) “, 0”無效(熄滅) ,當輸入數據從000H 到3FFH 變化時,點亮時間在0t~1 023t 變化,而亮度控制總時間則保持不變,從而實現了10 位占空比控制,采用這種灰度控制方法可以實現1 024 級的灰度顯示。與“19 場掃描”原理不同,本文控制點亮的時間不是通過屏幕刷新來實現,而是采用單獨的計數器來進行計時控制的。

表2 逐位點亮控制中各位數據點亮時間分配表

設使用串行方式更新整場視頻圖像一位數據所需要的時間為Ts ,如果Ts 滿足:

則完成一次串行數據更新所需要的時間在Dn - 1位所需要的點亮時間和Dn 位的點亮時間之間,這個時間也許小于一個時間t。由于串行數據更新時間和點亮時間可以部分重疊,設屏幕的刷新率(即顯示數據幀從顯示緩存讀出進行屏幕顯示更新的頻率) 為f r ,可以得到式(3) 。

當串行時鐘頻率和屏體參數確定, Ts 便可計算出來。此時,如果設定了屏幕的刷新率,結合式(2) 和式(3) ,對n 從0~9 進行窮舉計算,可以得到同時滿足兩式條件的n 值,同時可以確定單位時間t 的值。由此得到的t 值,通過FPGA 進行定時控制,便可實現一定刷新率的全彩灰度控制。

這里LED 的發光效率可以用式(4) 表示。

從式(3) 可知,當串行移位時鐘頻率一定,即Ts 確定的情況下,刷新率f r 與單位時間t 成反比。而式(4) 表明,發光效率η和單位時間t 成正比。可見,刷新率和發光效率成反比關系,提高刷新率的同時必然要犧牲發光效率。因此,采用上述掃描方式,設計者可以根據實際應用環境和客戶的要求在刷新率和發光效率兩者之間進行適當的調整。

如果要求系統的全彩灰度控制符合“19 場原理”的顯示效果,則由表2 可得表3 所示的關斷時間t0 ~t9 的值。結合表3 中t0 ~ t9 的值,對表2中總時間各項進行求和,便可得總時間為Ta =1 152t ,根據1 152t = 1/ f r 可得到t 值。

表3 逐位點亮控制中符合“19 場掃描”時各位數據關斷時間分配表在系統設計中,掃描板每個輸出端口分別控制16 ×48 分辨率的靜態顯示屏模塊,紅、綠、藍三色顯示數據采用3 根數據線分別輸出,串行移位時鐘頻率為6. 25 MHz ,顯示屏刷新頻率設計要求為120 Hz ,利用以上的結論可得:

Ts = 16×48×16125×106 s = 122188μs然后進行窮舉計算,如表4 所示,可以得到單位時間t 的值為7. 780μs。

表4 對n 進行窮舉計算得到單位時間t 的值根據式(4) ,可計算得到發光效率η = 1023tf r = 1023 ×71780 ×10- 6 s ×120Hz = 9515 %

3 FPGA 電路設計

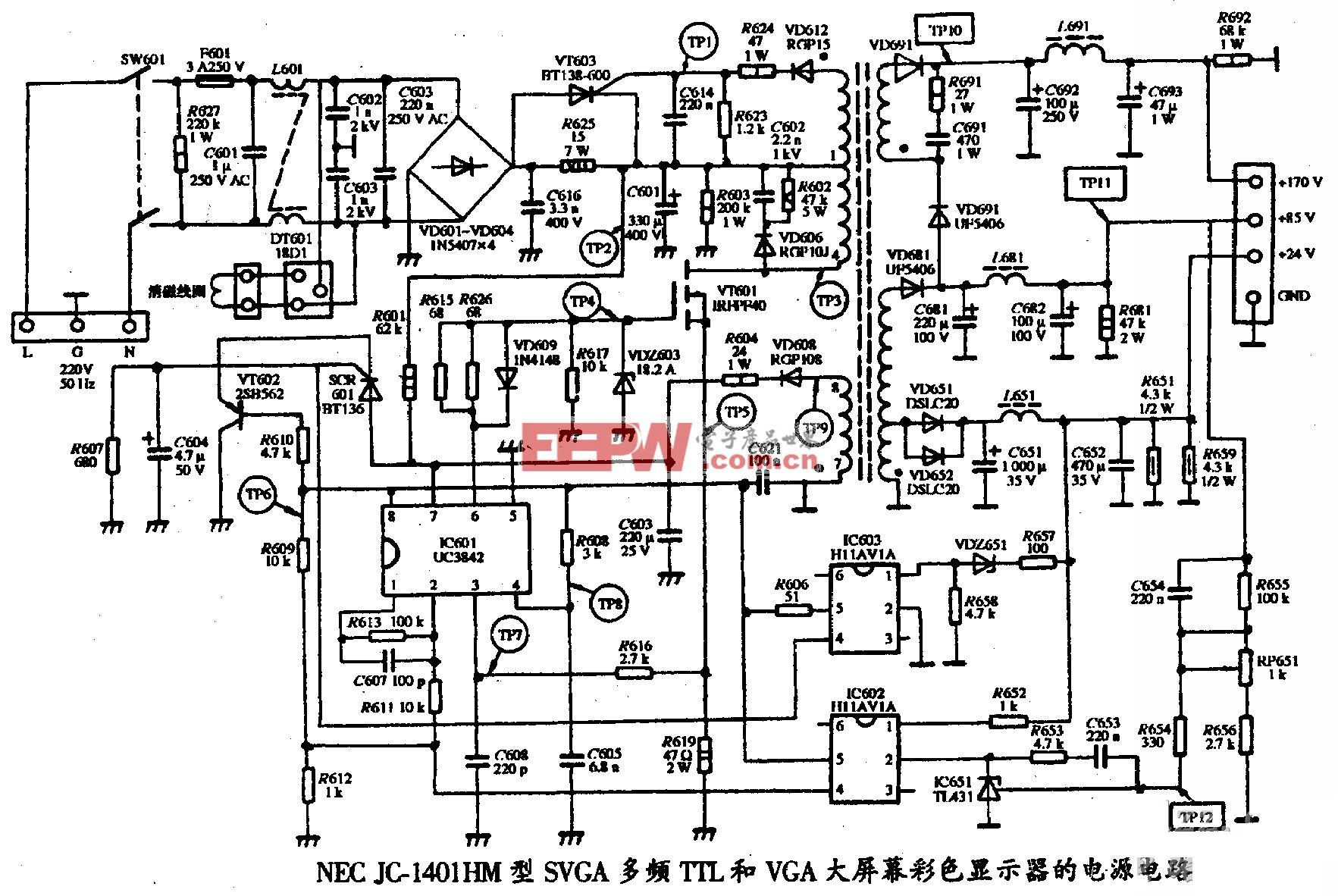

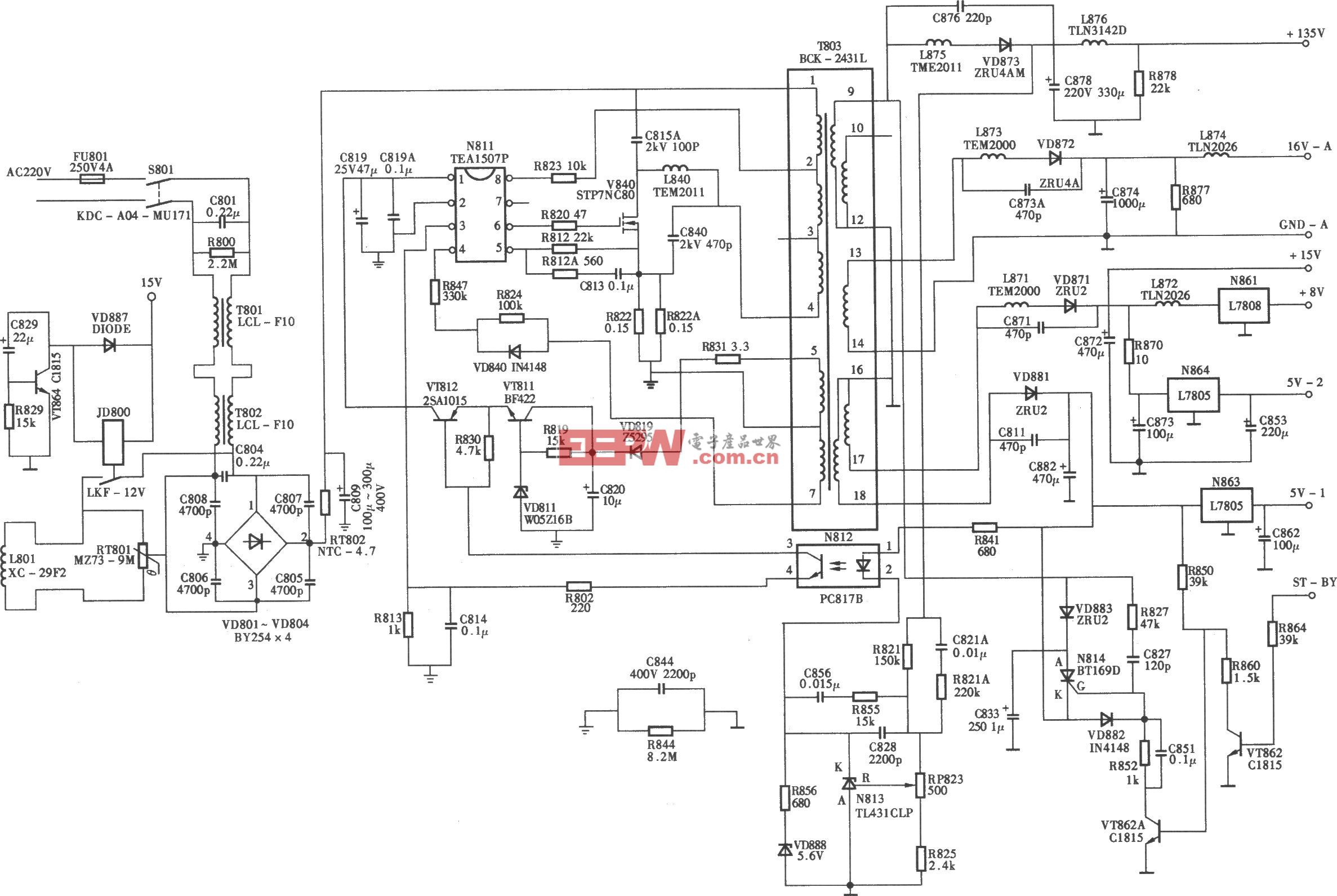

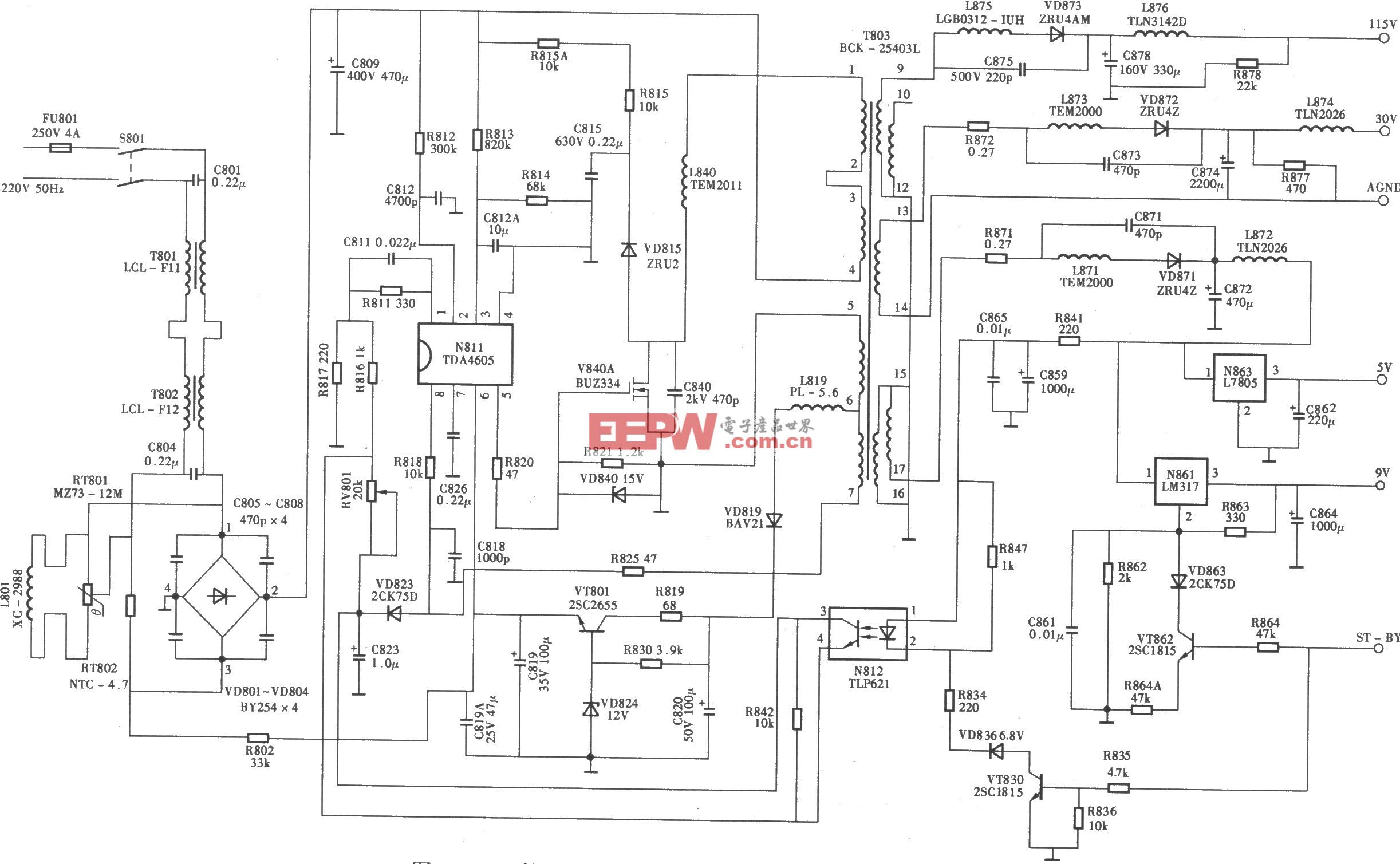

視頻圖像信號頻率高、數據量大,要求實時處理,加之全彩大屏幕LED 控制器實現的數字邏輯相當復雜,采用CPLD/ FPGA 設計控制電路,可以簡化系統結構,便于調試。本文設計的掃描控制器應用于大屏幕全彩LED 脫機視頻播放系統中。其中涉及到視頻信號的存儲和讀取、視頻數據的傳輸和接收、灰度顯示控制電路、LED 點陣顯示驅動電路等。本文主要對灰度顯示控制電路進行討論,控制對象為以紅、綠、藍三色LED 組成的全彩靜態顯示屏。實現灰度顯示控制器的FPGA 內部電路結構如圖1 所示。

在LED 顯示屏掃描控制電路中,FPGA 是其中最主要的邏輯控制器件,主要實現視頻數據接收、非線性灰度校正和掃描信號產生功能。FP2GA 內部各個電路模塊相互協調運作,將數據輸入和顯示輸出連接起來,實現L ED 顯示屏的全彩視頻播放。

作為一個獨立的顯示系統,普通的RS232 、RS485 總線方式已不能滿足L ED 顯示屏進行多媒體視頻播放所要達到的高數據速率傳輸要求。以512 ×256 的全彩顯示屏為例,當要求系統換幀頻率達到30 Hz 時,需要的數據傳輸速率高達94. 4 Mbp s。因此,在系統設計中,視頻數據的傳輸和接收采用RTL8201 設計的100 M 以太網控制器來完成。

為了使視頻播放連續平滑,在數據接收過程中不能打斷顯示

評論