基于FPGA多路機載冗余圖像處理系統的設計方案

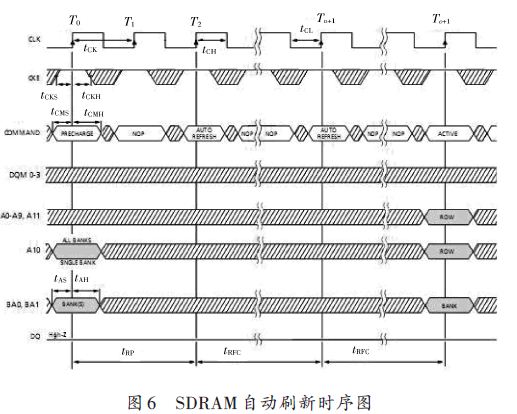

SDRAM在完成讀寫操作的同時還需要完成每64 ms全行(4 096行)自動刷新操作,為所有行進行充電,不然就會導致SDRAM內的數據丟失。自動刷新時序圖如圖6所示。

本文引用地址:http://www.j9360.com/article/221481.htm

這里將自動刷新操作穿插在讀寫當中,經計算為15 μs 需進行一次自動刷新操作,通過一個計數器每15 μs 發起一次自動刷新請求,程序檢測到自動刷新操作請求后進行自動刷新操作然后再進行讀寫操作,自動刷新操作占用10個時鐘周期。圖7為寫和讀之間穿插了一次自動刷新操作,操作命令為10001.

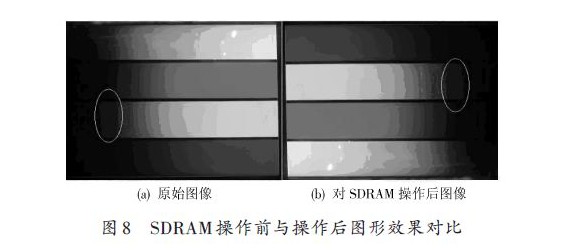

測試結果證明,該緩存系統實現了預定功能,可以對視頻數據進行更方便的操作與管理。SDRAM操作前與操作后圖形效果對比如圖8所示。

4 結語

本文介紹了某機載實時冗余視頻圖形處理系統的設計方案,該系統利用FPGA設計結構化狀態機實現對 SDRAM的控制,完成了對數據的緩存設計,實現了對多路DVI視頻冗余信號的解碼、編碼、實時處理以及輸出顯示。該系統電路設計簡潔,具有速度快、可靠性高、靈活性強和功能可擴展等優點。并且,由于信號通道增加冗余設計,因而加強了系統顯示的穩定性和可靠性。本系統已經投入使用,其性能可靠、穩定,實用性強。該方法值得推廣。

評論