MPEG算法在列車運行監控系統中的應用

1 硬件系統組成

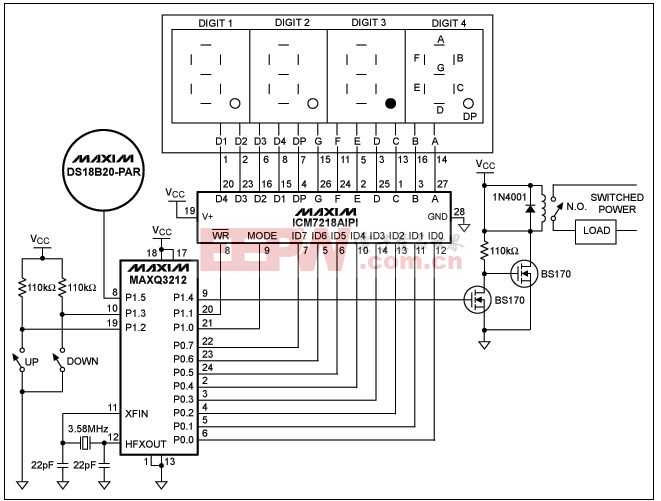

該監控記錄設備總體結構如圖1所示,整個系統由A/D轉換芯片、數字信號處理器DSP、CPLD控制器、Flash大容量存儲器及LCD顯示屏等組成。

在本系統中A/D轉換芯片用來完成信號的轉換,數據格式在16、18、20bit之間可選;數字信號處理器(DSP)為系統的核心數字處理器,功能強大,完成數字信號的壓縮編碼;CPLD用于數據傳送的控制以及對A/D轉換器、Flash存儲器和LCD顯示屏等器件的初始化檢測設置;Flash大容量存儲器用來進行數據的存儲;LCD顯示屏用來顯示當前系統所處的狀態,如運行等待、數據處理等。系統上電后,若有音頻/語音信號輸入A/D轉換器,通過中斷、查詢判斷輸入的信號類別,之后進行音頻/語音信號的模擬/數字格式轉換,得到的一串數字信號送入DSP進行數據壓縮編碼后,經由CPLD存儲到Flash大容量存儲器中。整個系統以流水線的方式工作,數據的采集、壓縮編碼、存儲同時進行。

1.1 音頻/語音處理器UDA1341TS

UDA1341TS是由Philips公司生產的一款單片立體聲A/D、D/A轉換器,低功耗,工作電壓3.0V,信噪比為97dB,具有雙通道輸入功能,采樣頻率在16kHz、32kHz和44.1kHz之間可選。

UDAl341TS與DSP構成音頻/語音信號采集系統,主要涉及到位采樣時鐘(BCK)、字同步時鐘(WS)、采樣數據輸出(DATA0)、系統時鐘輸入(SYSCLK)這幾個對時序有要求的引腳。系統中,DATA0作為輸出引腳,與DSP的BDR0引腳相連;BCK、WS、SYSCLK作為輸入引腳,其時序由DSP供給。UDA1341TS的系統時鐘只能是256Fs、384Fs、512Fs,通過對狀態寄存器的SC0位和SC1位編程可實現系統時鐘的選擇設置。這里Fs是音頻/語音信號的采樣頻率。在數據采樣時,WS用來指明UDA1341TS的DATAO輸出的有效數據。當系統對VINL(左聲道)端口進行采樣時,WS的上升沿表明一幀數據的起始,下降沿表明一幀數據的結束;當系統對VINR(右聲道)端口進行采樣時,WS的下降沿表明一幀數據的起始,上升沿表明一幀數據的結束。

UDA1341TS提供了一個L3端口,利用CPLD控制器對L3的L3DATA、L3MODE、L3CLOCK三個引腳進行編程,可以設置其內部的寄存器。當L3MODE引腳為低電平時,通過L3DATA引腳輸入寄存器地址信息;當L3MODE引腳為高電平時,通過L3DATA引腳輸入有關寄存器設置的數據信息(如設置芯片系統時鐘頻率、數據輸入格式、芯片工作模式等)。UDA1341TS與DSP的McBSP(多通道緩沖同步串口)相連,各種同步信號由DSP產生,這樣就保證了新數據的正常接收以及已接收數據的正常處理。UDA1341TS與DSP的硬件連接圖如圖2所示。

1.2 音頻/語音編碼器TMS320VC5402

數字音頻/語音信號的壓縮需要大量的數字信號處理,一般單片機是無法完成的,所以本系統中選用TI公司的DSP芯片TMS320VC5402(以下簡稱‘C5402)對音頻/語音信號進行壓縮處理。‘C5402是TI公司于1999年10月推出的54X系列定點DSP,操作速率達100MIPS,具有增強的多總線結構,三條獨立的16位數據存儲器總線和一條程序存儲器總線;40位的算術邏輯單元,包括兩個獨立的40位累加器、17位

評論