串行RapidIO: 高性能嵌入式互連技術

串行RapidIO(SRIO)針對高性能嵌入式系統芯片間和板間互連而設計,是未來十幾年中嵌入式系統互連的最佳選擇之一。

與傳統嵌入互連方式的比較

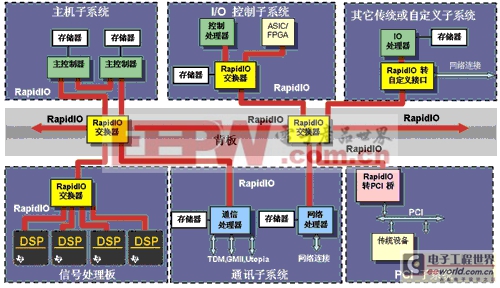

圖1展示了RapidIO互連在嵌入式系統中的應用。隨著高性能嵌入式系統的不斷發展,芯片間及板間互連對帶寬、成本、靈活性及可靠性的要求越來越高,傳統的互連方式,如處理器總線、PCI總線和以太網,都難以滿足新的需求。

圖1 RapidIO在嵌入式系統中的應用

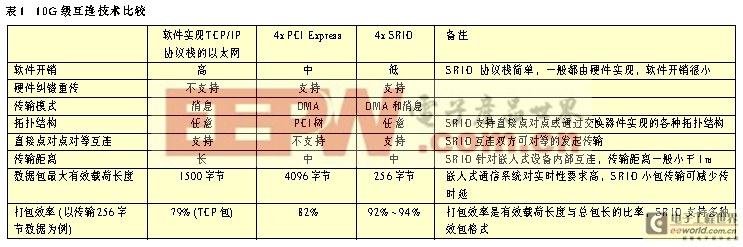

表1總結比較了的三種帶寬能達到10Gb/s的互連技術:以太網、PCI Express和串行RapidIO。可以看出串行RapidIO最適合高性能嵌入式系統應用。

串行RapidIO協議

RapidIO行業協會成立于2000年,其宗旨是為嵌入式系統開發可靠的、高性能、基于包交換的互連技術。串行RapidIO是物理層采用串行差分模擬信號傳輸的RapidIO標準。SRIO 1.x 標準支持的信號速率為1.25GHz、2.5GHz、3.125GHz;正在制定的RapidIO 2.0標準將支持5GHz和6.25GHz.

目前,幾乎所有的嵌入式系統芯片及設備供應商都加入了RapidIO行業協會。以德州儀器(TI)為例,TI 2001年加入該組織,2003年成為領導委員會成員。2005年底,TI推出第一個集成SRIO的DSP,后來又陸續推出共5款支持SRIO的DSP,這使得RapidIO的應用全面啟動。

RapidIO協議結構及包格式

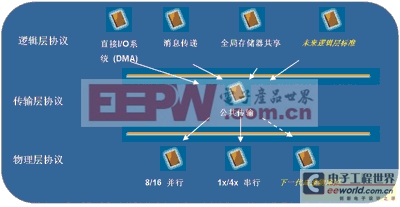

為了滿足靈活性和可擴展性的要求,RapidIO協議分為三層:邏輯層、傳輸層和物理層,如圖2所示。邏輯層定義了操作協議;傳輸層定義了包交換、路由和尋址機制;物理層定義了電氣特性、鏈路控制和糾錯重傳等。

圖2 RapidIO協議分層結構

評論