基于高速串行BCD碼除法的數字頻率計的設計

數字頻率計是計算機、通訊設備、音頻視頻等科研生產領域不可缺少的測量儀器。采用VDHL編程設計實現的數字頻率計,除被測信號的整形部分、鍵輸入部分和數碼顯示部分以外,其余全部在一片FPGA芯片上實現,整個系統非常精簡,而且具有靈活的現場可更改性。在不更改硬件電路的基礎上,對系統進行各種改進還可以進一步提高系統的性能。該數字頻率計具有高速、精確、可靠、抗干擾性強和現場可編程等優點。

在設計中,所有頻段均采用直接測頻法對信號頻率進行測量,克服了逼近式換擋速度慢的缺點;采用了門控信號和被測信號對計數器的使能端進行雙重控制,提高了測量的精確度;在運算單元采用了高速串行BCD碼除法,不僅提高了運算速度,而且減小了資源消耗。

1 系統結構及基本設計原理

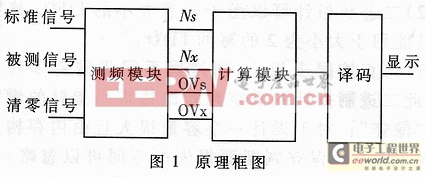

以一個8位十進制、測量范圍為1Hz~100MHz的數字頻率計為例,采用100MHz的標準頻率信號,說明設計的基本原理及實現。設計的數字頻率計由測量頻率模塊、計算模塊和譯碼模塊組成,如圖1所示。測頻模塊采用兩個十進制計數器分別測出門控時間內的標準信號和被測信號的周期數Ns和Nx。計算模塊則根據公式Fx/Nx=Fs/Ns算出Fx,通過譯碼即可得到被測信號頻率的7段數碼顯示。

數字頻率計的設計原理實際上是測量單位時間內的周期數。這種方法免去了實測以前的預測,同時節省了劃分頻段的時間,克服了原來高頻段采用測頻模式而低頻段采用測周期模式的測量方法存在換擋速度慢的缺點。

為克服低頻段測量的不準確問題,采用門控信號和被測信號對計數器的使能信號進行雙重控制,大大提高了準確度,如圖2所示。

當門控信號為1時,使能信號并不為1,只有被測信號的上升沿到來時,使能端才開始發送有效信號,兩個計數器同時開始計數。當門控信號變為0時,使能信號并不是立即改變,而是當被測信號的下一個上升沿到來時才變為0,計數器停止計數。因此測量的誤差最多為一個標準時鐘周期。當采用100MHz的信號作為標準信號時,誤差最大為0.01μs。

2 高速串行BCD碼除法運算原理

利用FPGA實現二進制除法運算,一種方法是采用逼近法,這種方法速度低、準確性不高。另一種方法是采取被除數與除數的倒數相乘的方法,即將除數作為寄存器的地址,其倒數的小數部分作為寄存器的內容,通過一次寄存器尋址來計算除數的倒數。這種方法在一個時鐘周期內即可完成一個完整的除法運算,雖然速度較高,但對于多字節除法運算,不僅程序復雜,而且占用資源較多。根據頻率計的實際情況,本設計采用串行除法運算,利用多個時鐘周期完成一個完整的除法運算,從而兼顧了頻率計對速度和資源兩方面的要求。

2.1 多位串行BCD碼減法原理

在數字串行除法運算中,減法運算是必不可少的部分。數字串行BCD碼的減法運算是將P位的BCD碼分為P個寬為4的二進制數,然后從低位開始相減,在P個時鐘周期內完成減法操作。如果輸入的操作數位數為8,那么串行BCD碼減法器可以在8個時鐘周期內完成8位BCD碼減法運算。

數字串行減法的控制也比較簡單,1位BCD碼減法運算完成,進行移位操作,并且移位次數加1,然后通過采用start信號指示新計算周期。當移位次數為n時,輸出移位寄存器完成串/并轉換,輸出結果。設計者可以根據實際情況,通過選擇不同的n,提高設計的靈活性。本設計選擇n=8。

該設計在提高速度的同時,節省了資源。實驗證明,采用1OOMHz的工作頻率,實現一個8位BCD碼串行減法運算,耗用的資源卻小于實現2位BCD碼并行減法運算所耗用的資源。

評論