單片機與CPCI總線的脈沖信號檢測系統設計

引言

在工業控制領域,通常有大量的脈沖信號用于控制其他設備或部件的開關或者工作狀態切換。這些脈沖信號除了常規計算機系統采用的+5 V接口電平外,還有+12 V、+30 V,乃至更高幅度的接口電平,通常為功率型電流驅動信號。本文提出了一種兩級測試系統的設計思路,給出了在較寬的范圍內兼容不同接口電平的脈沖信號檢測系統的設計方案,采用標準CPCI總線接口設計,具有良好的兼容性和擴展性,適用于產品功能測試或系統集成測試。

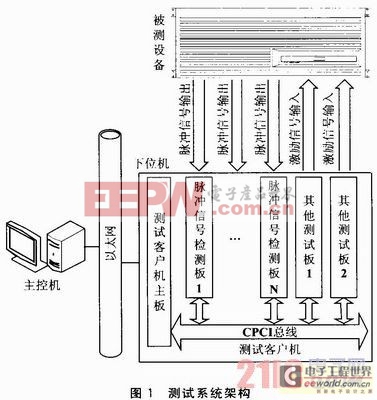

1 測試系統架構

如圖1所示,測試系統采用二級(主控機、下位機)結構設計,由主控計算機(即主控機)、測試客戶機(即下位機)、局域網、電纜及運行于各設備中的測試軟件共同構成。主控計算機屬主控機一級,控制測試客戶機,測試任務由主控計算機控制完成。測試客戶機控制其對應的測試設備可獨立完成設備級的功能測試。整個測試系統通過對被測設備施加激勵信號并檢測其響應輸出的方式,實現對被測沒備的閉環測試。

脈沖信號檢測板是工作于測試客戶機中的測試板卡,其主要功能是接收80路外部脈沖信號,測量并記錄每路脈沖信號的脈沖寬度及收到脈沖的時間。

2 脈沖信號檢測板實現方案

2.1 總體設計

脈沖信號特性為:脈沖持續時間為80~500 ms,偏差為±10 ms;驅動電流不小于200 mA。在產品功能測試及系統集成測試階段,主要考核脈沖信號功能的正確性,故脈沖信號檢測板用于檢測脈沖信號的發生時間及脈沖持續寬度,要求測量誤差不大于±1ms。

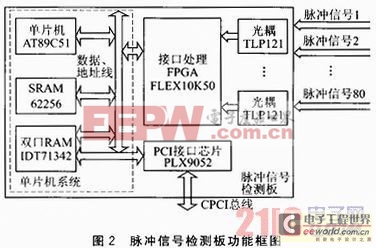

如圖2所示,脈沖信號檢測板的核心部分包括光耦接口電路、接口處理FPGA、單片機系統和PCI接口電路。板卡采用標準的6U尺寸CPCI板卡設計,兼容標準6U尺寸的CPCI工控機。

檢測板內部主要數據流向及處理流程為:80路脈沖信號通過光電耦合器(光耦)進行隔離變換,轉換成檢測板內部5 V電平信號;接口處理FPGA對信號進行采樣,并將80路脈沖采樣數據組幀緩存;單片機讀取FPGA中的采樣數據,并判斷是否檢測到有效脈沖信號,將檢測到的脈沖信號打上當前時間標簽后發送給雙口RAM;工控機軟件通過CPCI總線定期訪問雙口RAM,讀取數據。

2.2 脈沖信號接口

被測脈沖信號為功率驅動信號,用于驅動功率負載,驅動電流通常為幾mA至幾百mA,采用集電極開路門(OC)形式輸出,通常為+12~+30 V信號。為了兼容多種信號電平,并能隔離功率型信號與普通基帶電平信號,實現較好的電磁兼容性,本系統采用光電耦合器作為信號隔離與電平轉換的接口器件。

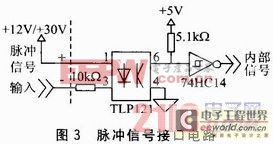

TLP121是東芝公司生產的光電耦合器,隔離阻抗為MΩ級,其前向驅動電流(IF)最大為20 mA,后端開關開啟和閉合時間均為μs級,可以滿足本系統對測量誤差不大于1 ms的要求。輸入接口電阻設為可調電阻,可適應不同輸入電壓。

脈沖信號接口電路如圖3所示。脈沖信號正線和回線連接至光耦的前端(圖3中TLP121的1、3引腳),后端(圖3中TLP121的4、6引腳)采用板內5V電源上拉,通過施密特電路74HC14整形后發送至接口處理FPGA。當脈沖信號有效時,光耦前端有電流流過,接口電路輸出高電平“1”;脈沖信號無效時,接口電路輸出低電平“0”。

評論