內嵌ARM核FPGA芯片EPXAl0及其在圖像驅動應用

隨著亞微米技術的發展,FPGA芯片密度不斷增加,并以強大的并行計算能力和方便靈活的動態可重構性,被廣泛地應用于各個領域。但是在復雜算法的實現上,FPGA卻遠沒有32位RISC處理器靈活方便,所以在設計具有復雜算法和控制邏輯的系統時,往往需要RISC

和FPGA結合使用。這樣,電路設計的難度也就相應大大增加。隨著第四代EDA開發工具的使用,特別是在IP核產業的迅猛發展下產生的SOPC技術的發展,使嵌入RISC的通用及標準的FPGA器件呼之欲出。單片集成的RISC處理器和FPGA大大減小了硬件電路的復雜性和體積,同時也降低了功耗、提高了系統可靠性。Altera公司的EPXAl0芯片就是應用SOPC技術,集高密度邏輯(FPGA)、存儲器(SRAM)及嵌入式處理器(ARM)于單片可編程邏輯器件上,實現了速度與編程能力的完美結合。本文所介紹的圖像驅動和處理系統正是應用了EPXAl0的這些特點,充分發揮了FPGA邏輯控制實現簡單、對大量數據做簡單處理速度快的優勢以及ARM軟件編程靈活的特點。

EPXAl0單片集成了ARM核、高密度的FPGA、存儲器及接口和控制模塊,不僅簡化了ARM與FPGA之間的通訊,也使片外擴展存儲器以及和外設通訊變得相對簡單;同時通過在FPGA中嵌入各種IP核和用戶控制邏輯可以實現各種接口和控制任務。這樣的高度集成化不僅大大加快了ARM與片內各種資源的通訊速度,而且減小了硬件電路的復雜性、體積和功耗,真正實現了SOPC。

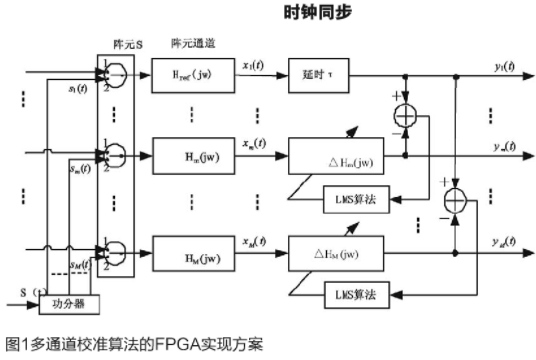

EPXAl0內部結構框圖如圖1所示式,主要分為嵌入處理器和FPGA兩部分。

1.1嵌入式微處理器ARM922T

EPXAl0嵌入式處理器部分集成了業界領先的32位ARM處理器(ARM922T),工作頻率可達200MHz;支持32位ARMv4T指令集和16位Thumb擴展指令集;具有全性能的內存管理單元以及8K的指令緩存和8K數據緩存,以支持實時操作系統(RTOS)、C語言和匯編語言。

1.2高密度的FPGA

EPXAl0片內FPGA部分具有1000000門可編程邏輯、3MB的內置RAM和512個可供用戶使用的I/0管腳,可以通過嵌入各種IP核實現各種標準工業接口(如PCI、USB等)。

1.3先進的存儲支持

EPXAl0嵌入式處理器部分集成了256KB單口SRAM和128KB雙口SRAM;同時集成了兩個先進的存儲支持:(1)SDRAM控制器,用于控制單倍速/雙倍速SDRAM。SDRAM的各種工作狀態是依據信號線上提供的不同控制時序來確定的,實現起來非常復雜。有了SDRAM控制器的支持,只需要在Altera公司提供的EDA開發軟件Quartus II中設置好SDRAM工作所需的各種參數,就可以按照直接給出指令、地址和數據的方式對SDRAM進行操作,控制器會自動將各種指令轉化成SDRAM所需的工作時序,大大降低了對SDRAM的控制難度。(2)擴展總線接口(EBl),可外接4個存儲設備,如閃速存儲器、SRAM等,總容量高達128MB。其中EBI接口0外接閃速存儲器,用于存儲用戶的軟件、硬件設計代碼。

1. 4方便的接口模塊

EPXAl0嵌入式處理器部分嵌入了串口通訊模塊(UART),可以不用編程直接實現ARM與超級終端之間的串行通訊,實時監視軟件的運行情況。如果要實現計算機與ARM之間的數據傳遞存儲,只需用戶編寫基于VC++語言的串口通訊程序,這需要用到Microsoft公司提供的MSComm串行通訊控件。

1.5靈活的啟動方式

EPXAl0共有兩種啟動方式:(1)從ARM啟動。這種啟動方式需要將設計下載到片外閃速存儲器中,而且設計中必須包含對ARM的應用。啟動時ARM為主動,配置各種寄存器及FPGA,執行軟件代碼。(2)從FPGA啟動。這種啟動方式需要將設計下載到片外E2PROM中,而且設計中可以只包含FPGA部分的應用。啟動時PP-GA為主動,ARM處于復位狀態,配置完成后,如果有對ARM的應用,則ARM解除復位,執行軟件代碼;反之,ARM一直處于復位狀態。

評論