基于ARM9處理器的嵌人式音頻系統設計

隨著 Internet技術和多媒體技術的快速發展,語音通信技術的應用越來越廣泛,也越來越受到重視[1]。如今的嵌人式設備日益復雜化,功能比以前更加豐富,性能也越來越高。在多種嵌人式終端產品中,音頻處理功能已成為不可缺少的重要組成部分,高質量的音效是當前發展的重要趨勢。

本文利用 ATMEL公司 的 AT91RM9200型微處理器 和 Philips公司的 UDA1341型立體聲音頻編解碼器設計了一種嵌入式音頻系統。該嵌入式音頻系統硬件部分采用基于IIS總線的音頻系統體系結構,其主要硬件電路后文作了詳細的介紹。軟件上,筆者以嵌入式Linux操作系統作為平臺,重點介紹該音頻系統在此平臺下的驅動程序的實現。

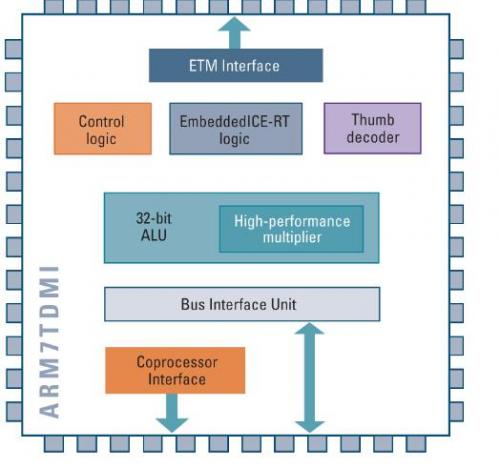

2 AT91RM9200處理器簡介

AT91RM9200是 ATMEL公司針對系統控制以及通信領域推出的基于ARM920T內核的新型微處理器[2],在高性能和低功耗特性方面具有極大的優勢,而且具有很高的主頻,最高可達到180 MHz。該處理器具有獨立的16K指令和16K數據cache,全功能的MMU虛擬內存管理單元,以及內部的16KB SRAM和128KB ROM,EBI接口控制器。片上集成了豐富的外圍接口,包括網絡MAC、USB控制器、SDRAM 控制器、CF接口、NAND flash接口、IIC接口、JTAG調試器以及支持 256 MB的地址空間。而且處理器還提供自舉模式,供用戶寫入引導代碼,方便 Linux等操作系統的移植。

3 UDA1341TS音頻芯片及IIS總線簡介

Philips公司的 UDA1341TS是一塊功能強大的專用語音處理芯片[3]。該芯片集語音放大、濾波、采樣、A/D和D/A轉換等功能于一體,并且能進行數字語音處理。本設計使用的AT91RM9200處理器具有一個IIS音頻接口,此接口采用 DMA方式傳輸數據。在該方式下,由DMA控制器取代CPU,獲得總線控制權,從而實現內存與外設或者內存之間的不同區域之間大量數據的快速傳輸。用DMA接口傳輸數據,不僅可以降低CPU負擔,還可以節省系統的軟件設計時間,降低編程難度。而 UDA1341TS支持IIS總線格式,并且具有數字語音處理特性,由此決定了UDA1341TS與AT91RM9200處理器的電路連接比較簡單,并且能實現語音的 A/D和 D/A等預處理,而不需要再額外增加專門的A/D和 D/A器件。

需要說明的是,數字音頻系統需要多種多樣的集成電路,因此,為這些電路提供一個標準的通信協議非常重要。IIS總線是由SONY和PHILIPS公司等電子巨頭共同提出的數字音頻總線協議,全稱是內部集成電路聲音總線 (Inter IC Sound Bus),它是一種串行的數字音頻總線協議,該總線專門用于音頻設備之間的數據傳輸,為數字立體聲提供一個序列連接至標準編解碼器[4],目前很多音頻芯片和處理器都提供了對IIS總線的支持。筆者根據IIS總線的原理,結合AT91RM9200處理器和數字音頻輸入/輸出接口芯片 UDA1341TS的結構特點,設計的嵌入式音頻系統可以運用到很多類似的音頻系統中。

4 系統硬件設計方案

由于IIS總線只處理音頻數據,而其他的信號如編碼、控制等信號單獨傳送。為了使必需的引腳數最小并且保持連線簡單,IIS總線由3條信號線組成:時分復用的數據通道線、字段選擇線和時鐘信號線。本系統由系統主控制器提供時鐘信號,控制數字音頻數據在各個IC之間的流向。此時,發送器在外部時鐘信號的控制下產生數據,處于從模式。

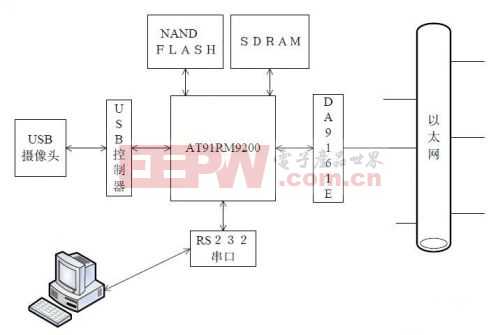

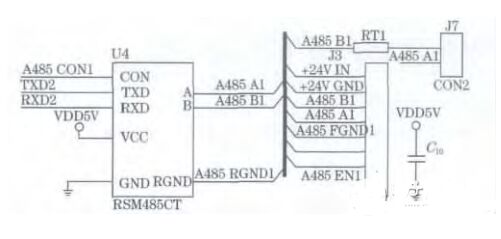

本設計硬件連接圖比較簡單,如圖1所示。圖中的處理器采用了AT91RM9200處理器,其內置IIS音頻總線,內置的IIS接口能讀取IIS總線上的數據,并由UDA1341TS芯片外擴,通過總線和系統連接,需要處理器提供系統時鐘和3根控制線。

圖1 硬件設計簡圖

AT91RM9200的IIS控制器由5個引腳與外部的音頻編解碼器相連。這些引腳分別是:系統時鐘;位速率時鐘(可使用內部或外部時鐘源);字段選擇;串行聲音輸入;串行聲音輸出。本設計中,UDA1341TS使用的是L3接口 ,該接口用來控制音頻信號的音量大小以及低音等。L3接口有3個信號:L3MODE,L3CLK,L3DATA,將字節寫入 L3總線寄存器。IIS總線控制器通過軟件控制AT91RM9200的通用I/O引腳(筆者選用的是PA0、PA1、PA2三個通用I/O口)來支持L3接口。下圖是本嵌入式音頻系統的硬件電路連接圖,見圖2

評論