C8051F單片機實驗系統設計方案

2.3 SRAM模塊

C8051F020內部有位于外部數據存儲器空間的4 096字節的片上RAM,還有外部數據存儲器接口EMIF,可用于訪問片外存儲器和存儲器映射的I/O器件。外部數據存儲器接口EMIF可配置到低I/O端口P0~P3,也可配置到高I/O端口P4~P7。而且,既可以配置為數據、地址復用方式,也可以配置為非復用方式。若要節省端口I/O,可采用數據、地址復用方式,能節省8根端口線,但是速度較慢,若要提高速度,則可

以采用非復用方式。

2.3.1 配置外部存儲器接口的步驟

1)將EMIF選到低端口(P3~P0)或選到高端口(P7~P4)。

2)選擇復用方式或非復用方式。

3)選擇存儲器模式(只用片內存儲器、不帶塊選擇的分片方式、帶塊選擇的分片方式或只用片外存儲器)。

4)設置與片外存儲器或外設接口的時序。

5)選擇所需要的相關端口的輸出方式。

在本系統中考慮到(28051F020單片機的PO~P3口大部分為功能復用引腳,為使單片機的資源得到最大的開發,將單片機的高端I/O口,即P4~P7接入FPGA,并通過FPGA對RAM進行訪問。將單片機配置為高端口(P4~P7)、地址/數據總線分時復用方式,FPGA控制RAM的片選、讀/寫等操作,其中注意FPGA、單片機、RAM的時序統一問題。

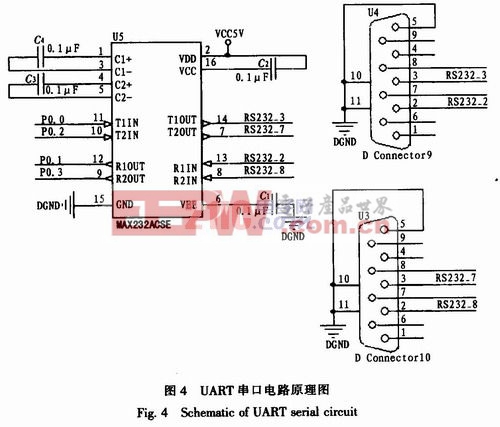

2.4 UART串口

UART是一種通用串行數據總線,該總線雙向通信,可以實現全雙工傳輸和接收。在嵌入式設計中,UART用來與PC進行通信,包括與監控調試器和其他器件,如EEPROM通信。

UART首先將并行數據轉換成串行數據來發送。消息幀從一個低位起始位開始,后面是若干數據位,一個可用的奇偶校驗位和一個高位停止位。接收器發現開始位時它就知道數據準備發送,并嘗試與發送器時鐘頻率同步。在接收過程中,UART從消息幀中去掉起始位和結束位,對進來的字節進行奇偶校驗,并將數據字節從串行轉換成并行。UART也產生額外的信號來指示發送和接收的狀態。例如,如果產生一個奇偶錯誤,UART就置位奇偶標志。

C805lF020單片機中有兩個增強型串行口:UART0和UARTl。所謂增強型是指,這兩個串口都具有幀錯誤檢測和通信地址硬件識別功能。它們都可以工作在全雙工異步方式或半雙工同步方式,并且支持多處理器通信。開發板外擴兩個增強型UART串口,實現單片機與PC機、單片機和單片機之間的通信。其電路連接如圖4所示。

評論