關于串口FIFO中斷

串口的接收模塊包括接收緩沖寄存器和移位寄存器。接收的數據進入移位寄存器后經移位處理并行傳入緩沖寄存器,事實上,UART的FIFO是一個硬件環形的緩沖隊列,物理上不可尋址,不可見,僅U0RBR這個FIFO出口可見。U0RBR就是接收FIFO的第一位。FIFO的長度是可設的,也叫觸發點,低于這個長度的字符串不會引起中斷,但在實際應用中,不可能串口讀入的數據長度總為觸發點值的整數倍,為此,引入了CTI即字符接收超時中斷,當有不足觸發點值規定的字符串讀入時,將引起中斷,其與串口的RDA中斷具有相同的優先級,并會同時被使能。

那么,LPC2000的UART機制是如何判斷串口讀入數據的一次性容量呢?如果接收FIFO里已經有了1個字符,它可在一定的時間內等待下一個字符的讀入,也就是說,不超過一定的時間就不會觸發CTI中斷,這個時間是在本次通訊協議設置的前提下,接收3.5到4.5個字符所用的時間。比如,需串口接收GPRS數傳狀態成功建立后的返回值“Ok_Info_WaitingForData”22個字符組成的字符串,FIFO觸發點設置為14,在前14個字符讀入之后,立即觸發RDA中斷(接收中斷),跳轉至RDA中斷服務子程序將這14個字符放入我所預設的緩沖區內,接著,后8個字符讀入,這時CPU并不立刻中斷,它需等待在本次串口通訊協議設置的前提下,接收3.5到4.5個字符所用的時間(需根據波特率和幀格式具體計算),這個時間一到,立刻觸發CTI中斷(超時中斷),換句話說,超過這個時間的等待,CPU就認為一個完整的字符串已經結束了,這才是字符串超時的真正含義。

CTI觸發的前提是接收FIFO里已經有了1個字符,在等待下一個字符的進入

用FIFO發送數據時,需要保證接受端的FIFO不溢出,則發送過快,接受端FIFO滿后中斷末取走數據,發送端就又發數據。其只能由發送端來保證

不過接受端FIFO有2個Buffer,循環接收.

3、個人覺得,當FIFO的觸發深度設為1時和不用FIFO時的效果是一樣的。

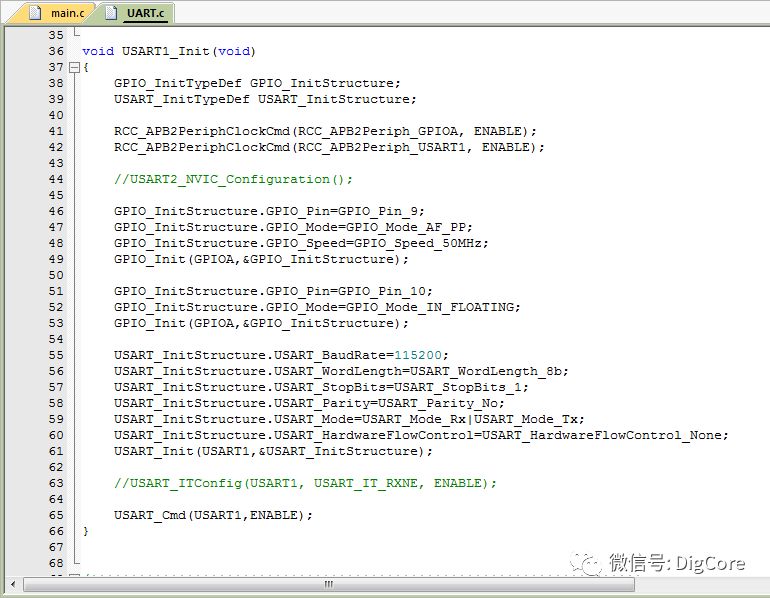

4、串口發送時,推薦第一個字符要在打開串口中斷前送(不懂???),否則可能中斷只來一次。比如下面的這個用串口中斷發送字符串的函數為:

/******************************************************

** 函數名稱 :UART0_SendStr()

** 函數功能 :向串口發送字符串

** 入口參數 :str 要發送的字符串的首地址指針

** 出口參數 :無

*******************************************************

void UART0_SendStr( CHAR const *str)

{

Str_Send_P = str;

U0THR = *Str_Send_P++;

U0IER |= 0x02; //開發送中斷

}

在中斷發送程序中的處理為:

SWITCH(IIR 0x0e)

{

case 0x02: //利用串口發送中斷,發送字符串

if((*Str_Send_P)!='')

U0THR = *Str_Send_P++;

else

U0IER = (~0x02); //關發送中斷

break;

這種做法的道理不太明白,但實驗證明,不這么做就只發一次!~

評論