51單片機復位電路的設計

單片機在可靠的復位之后,才會從0000H地址開始有序的執行應用程序。同時,復位電路也是容易受到外部噪 聲干擾的敏感部分之一。因此,復位電路應該具有兩個主要的功能:

1. 必須保證系統可靠的進行復位;

2. 必須具有一定的抗干擾的能力;

一、復位電路的RC選擇

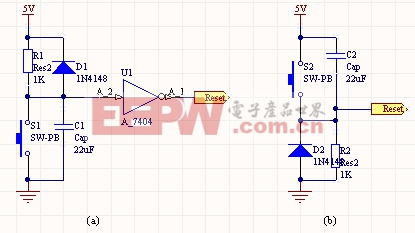

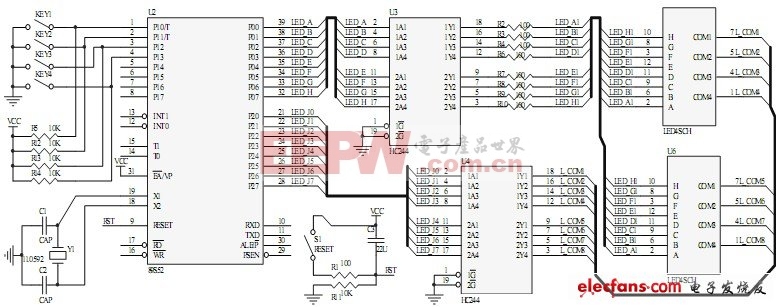

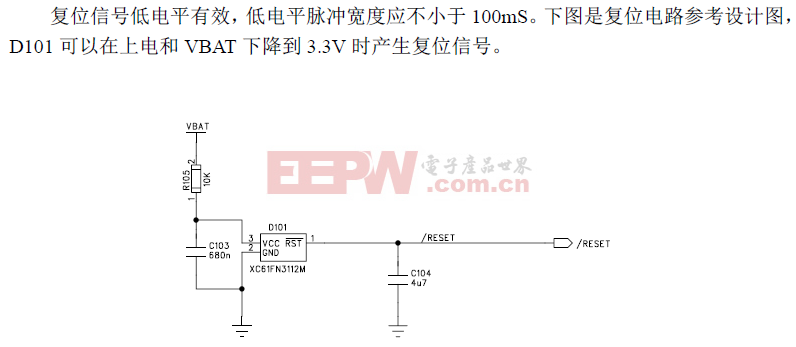

復位電路應該具有上電復位和手動復位的功能。以MCS-51單片機為例,復位脈沖的高電平寬度必須大于2個機器周期,若系統選用6MHz晶振,則一個機器周期為2us,那么復位脈沖寬度最小應為4us。在實際應用系統中,考慮到電源的穩定時間,參數漂移,晶振穩定時間以及復位的可靠性等因素,必須有足夠的余量。圖1是利用RC充電原理實現上電復位的電路設計。實踐證明,上電瞬間RC電路充電,RESET引腳出現正脈沖。只要RESET端保持10ms以上的高電平,就能使單片機有效的復位。

圖 1

對于圖1-a中的電容C兩端的電壓(即復位信號)是一個時間的函數:

u(t)=VCC*[1-exp(-t/RC)]

對于圖1-b中的電阻R兩端的電壓(即復位信號)也是一個時間的函數:

u(t)=VCC*exp(-t/RC)

其中的VCC為電源電壓,RC為RC電路的時間常數=1K*22uF=22ms。有了這個公式,我們可以更方便的對以上電路進行透徹的分析。

圖1-a中非門的最小輸入高電平UIH=2.0v,當充電時間t=0.6RC時,則充電電壓u(t)=0.45VCC=0.45*5V,約等于2V,其中t即為復位時間。圖a中時間常數=22ms,則t=22ms*0.6=13ms。

二、復位電路的可靠性與抗干擾性分析

單片機復位電路端口的干擾主要來自電源和按鈕傳輸線串入的噪聲。這些噪聲雖然不會完全導致系統復位,但有時會破壞CPU內的程序狀態字的某些位的狀態,對控制產生不良影響。

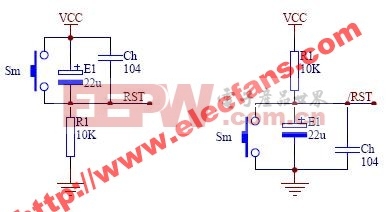

1.電路結構形式與抗干擾性能

以圖1為例,電源噪聲干擾過程示意圖如圖2種分別繪出了A點和B點的電壓擾動波形。

有圖2可以看出,圖2(a)實質上是個低通濾波環節,對于脈沖寬度小于3RC的干擾有很好的抑制作用;圖2(b)實質上是個高通濾波環節,對脈沖干擾沒有抑制作用。由此可見,對于圖1所示的兩種復位電路,a的抗干擾電源噪聲的能力要優于b。

2. 復位按鈕傳輸線的影響

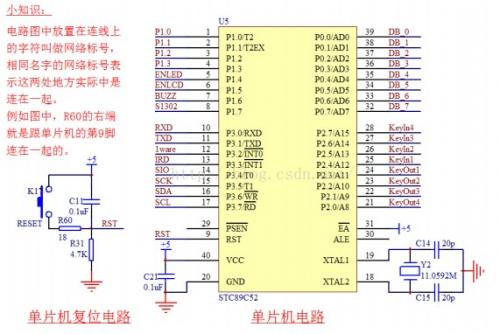

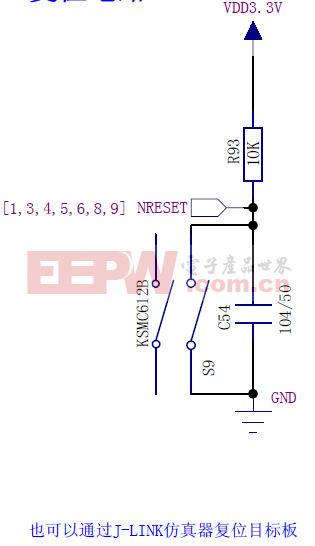

復位按鈕一般都是安裝在操作面板上,有較長的傳輸線,容易引起電磁感應干擾。按鈕傳輸線應采用雙絞線(具有抑制電磁感應干擾的性能),并遠離交流用電設備。在印刷電路板上,單片機復位端口處并聯0.01-0.1uF的高頻電容,或配置使密特電路,將提高對串入噪聲的抑制能力。

電路相關文章:電路分析基礎

51單片機相關文章:51單片機教程

單片機相關文章:單片機教程

單片機相關文章:單片機視頻教程

單片機相關文章:單片機工作原理

雙絞線傳輸器相關文章:雙絞線傳輸器原理

評論