基于ATmega48的串口轉FSK通信模塊設計

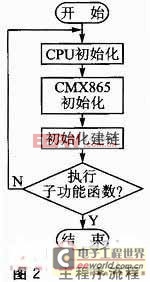

4.1 主程序實現流程

通信模塊主程序包括:CPU初始化、CMX865初始化、初始化建鏈、串口通信和FSK通信子程序等。主程序流程如圖2所示。初始化建鏈環節是模塊正常工作的基礎,通過初始化建鏈操作,信息終端可以根據線路環境以及平臺超時機制對通信模塊參數進行設置,確保通信的穩定性。通信主流程循環執行3個子功能函數:線路狀態處理函數、串口數據解析與處理函數、鏈路保持函數。線路狀態處理函數設計了3種線路狀態,即初始狀態、空閑狀態和摘機狀態;正常工作時僅在空閑狀態和摘機狀態之間切換。其中在空閑狀態檢測振鈴、根據狀態位執行摘機、DTMF撥號等操作;在摘機狀態根據狀態位執行FSK收發、脫線檢測、掛機控制等操作。串口數據解析與處理函數包含串口數據按命令集解析、對解析命令進行應答和狀態置位處理部分。這樣線路狀態處理函數和串口數據解析與處理函數通過狀態置位標志緊密連接起來。FSK數據采用中斷方式直接接收,接收完畢后在摘機狀態下直接通過串口發送給信息終端。由于串口發送應用相對單一,為簡單處理串口發送采用即時應答處理方式,分散在通信主流程各子功能函數中實現,提高了通信效率。通過鏈路保持函數判斷串口通信是否異常,通信模塊周期性地向信息終端發送鏈路保持命令,如果3次重發均未收到終端應答命令,通信模塊將自動鎖閉線路,重新執行初始化建鏈操作,實現串口異常的處理。

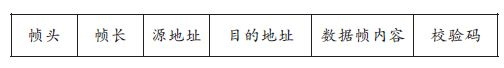

4.2 對外串口通信協議

模塊采用標準串口通信,波特率為19 200 bps,10位異步方式。定義串口通信數據包格式為:0x1E+命令+校驗和反碼(對命令的校驗和反碼),其中部分命令以變長方式發送。串口通信主要命令有:模塊初始化、鏈路保持、DTMF接收/發送、FSK接收/發送、振鈴、掛機等,命令具體格式和描述此處不加詳述。模塊初始化上電后由通信模塊自動發起,直到正確接收到終端應答初始化命令后,通信模塊才建鏈成功。信息終端初始化應答命令主要提供FSK通信模塊參數配置信息。上電后如果FSK模塊未收到終端初始化應答信息,則周期性地(每2 s)發送一次初始化建鏈命令,直到成功為止;模塊FSK通信過程中周期性地向終端發送鏈路保持命令,如果未收到終端應答信息,則斷開FSK鏈接重新開始模塊初始化。

4.3 串口通信實現

AVR單片機串口通信往往采用SPI通信方式,通信模塊串口通信采用UART0控制/狀態寄存器和數據寄存器實現。串口通信子程序主要由串口發送/接收中斷子程序、串口接收命令解析子程序和串口組包發送子程序3部分組成。其中串口中斷接收程序為:

具體執行串口數據發送時,需要提供發送數據長度、發送起始地址、置UCSROB寄存器值(UCSR0B |=0x28)。串口接收命令解析子程序按照對外串口通信協議解析串口命令,并根據命令描述調用子程序代碼執行相應子功能操作。為了通信容錯處理,通信模塊需對接收串口數據進行校驗,如果解析的串口命令格式正確,則向終端發送肯定應答;否則發送否定應答,等待終端重傳命令數據。串口組包發送子程序對接收的FSK數據以及線路狀態等信息數據,按照串口通信協議組包發送給信息終端。

4.4 FSK通信實現

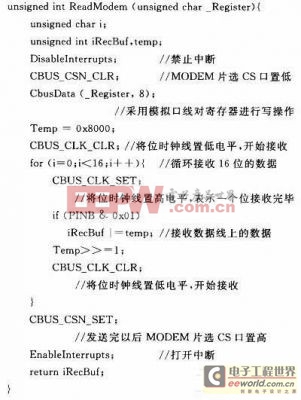

FSK通信子程序主要由CMX865芯片寄存器操作、FSK收/發、DTMF收/發以及線路狀態檢測等子程序組成。ATmega48芯片采用模擬口線的方式對CMX865寄存器進行讀/寫操作,其中對CMX865芯片寄存器讀操作程序為:

FSK收/發、DTMF收/發子程序均以CMX865寄存器讀/寫操作函數為基礎,通過設置CMX865寄存器的值,確定其工作模式。FSK數據發送、接收都可以通過CMX865芯片的IRQ中斷口線引起ATmega48芯片中斷,因此FSK數據收/發都通過中斷實現。芯片程序采用10 ms定時器循環檢測線路狀態。

結語

本文利用ATmega48芯片和CMX865芯片為硬件架構設計了串口轉FSK通信模塊。由于ATmega48芯片與ATmega88芯片除了Flash、EEPROM、SR AM容量差異外,性能完全相同。通信模塊可以不更改硬件電路,僅配置相應AVR芯片,對軟件稍作調整,能夠滿足通信業務對通信數據量增加的需求,節約模塊二次開發的成本。目前本通信模塊已在一款新型的電子交易終端上使用,并與中興、精倫等電子交易平臺進行信息交互,運行效果良好。

數字通信相關文章:數字通信原理

通信相關文章:通信原理

分頻器相關文章:分頻器原理

評論