基于ATmega8的DDS信號發生器的設計

1引言

頻率源是雷達、通信、電子對抗與電子系統實現高性能指標的關鍵,很多現代電子設備和系統的功能都直接依賴于所用頻率源的性能,因此頻率源被人們喻為眾多電子系統的“心臟”。而當今高性能的頻率源均通過頻率合成技術來實現。頻率合成器是利用一個或多個標準信號,通過各種技術途徑產生大量離散頻率信號的設備。傳統的頻率合成器有直接模擬合成法與鎖相環合成法兩種。直接模擬合成法利用倍頻、分頻、混頻及濾波,從單一或幾個參考頻率中產生多個所需的頻率。該方法頻率轉換時間快(小于100ns),但是體積大、功耗大,目前已基本不被采用。鎖相環式頻率合成器具有很好的窄帶跟蹤特性,可以很好地選擇所需頻率的信號,抑制雜散分量,并且避免了大量的濾波器,有利于集成化和小型化。但存在高分辨率和快轉換速度之間的矛盾,一般只能用于大步進頻率合成技術中。

直接數字頻率合成(DDS)是近年來發展起來的一種新的頻率合成技術。其主要優點是相對帶寬很寬、頻率轉換時間極短(可小于20ns)、頻率分辨率很高、全數字化結構便于集成、輸出相位連續、頻率、相位和幅度均可實現程控。因此,能夠與計算機緊密結合在一起,充分發揮軟件的作用。作為應用,現在已有DDS產品用于接收機本振、信號發生器、通信系統、雷達系統、跳頻通信系統等。

2DDS的基本工作原理

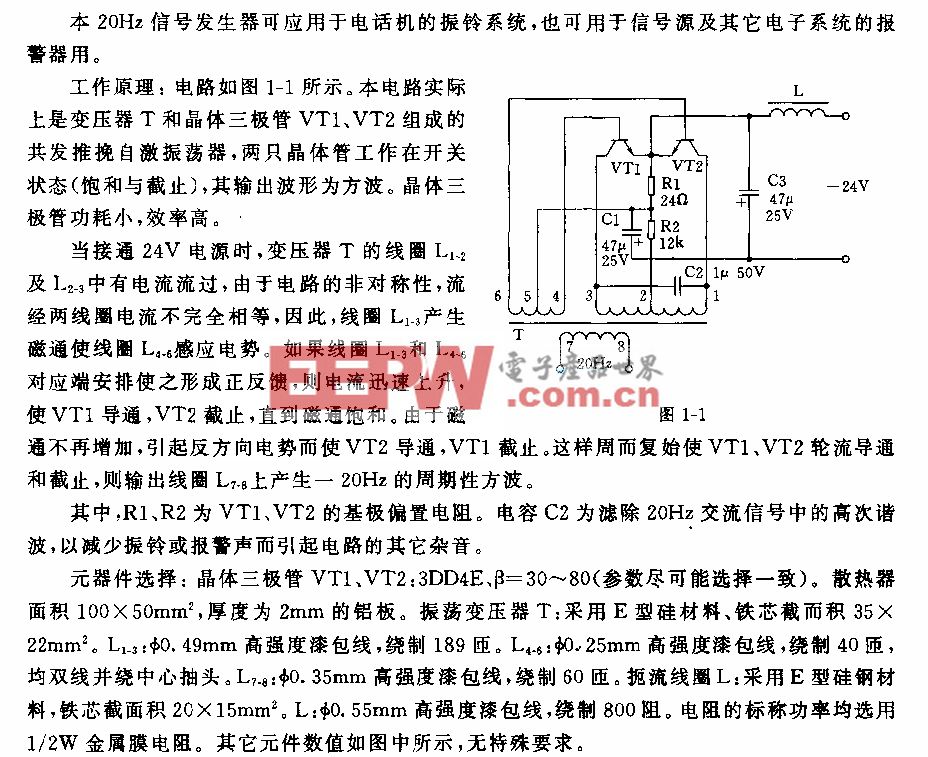

直接數字頻率合成是采用數字化技術,通過控制相位的變化速度,直接產生各種不同頻率信號的一種頻率合成方法。DDS的基本結構如圖1所示,它主要由相位累加器、正弦ROM表、D/A轉換器和低通濾波器構成。

參考時鐘fr由一個穩定的晶體振蕩器產生。相位累加器由N位加法器與N位相位寄存器級聯構成,類似于一個簡單的加法器。每來一個時鐘脈沖,加法器將頻率控制數據與相位寄存器輸出的累積相位數據相加,把相加后的結果送至相位寄存器的數據輸入端。相位寄存器將加法器在上一個時鐘作用后所產生的新相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘的作用下繼續與頻率控制數據相加。這樣,相位累加器在參考時鐘的作用下,進行線性相位累加,當相位累加器累積滿量時就會產生一次溢出,完成一個周期性的動作,這個周期就是DDS合成信號的一個頻率周期,累加器的溢出頻率就是DDS輸出的信號頻率。

在參考時鐘fr的控制下,頻率控制字由累加器累加以得到相應的相位數據,把此數據作為取樣地址,來尋址正弦ROM表進行相位-幅度變換,即可在給定的時間上確定輸出的波形幅值。DAC將數字量形式的波形幅值轉換成所要求合成頻率的模擬量形式信號,低通濾波器用于濾除不需要的取樣分量,這樣即可得到由頻率控制字決定的連續變化的輸出正弦波。

DDS的輸出頻率f0和參考時鐘fr、相位累加器長度N以及頻率控制字FSW的關系為: ; DDS的頻率分辨率為:

; DDS的頻率分辨率為: ;由于DDS的輸出最大頻率受奈奎斯特抽樣定理限制,所以DDS 的最高輸出頻率為fr/2,但在實際設計的DDS系統中,由于輸出濾波器的非理想性,一般輸出信號的最大頻率只能達到參考時鐘頻率fr的40%左右。

;由于DDS的輸出最大頻率受奈奎斯特抽樣定理限制,所以DDS 的最高輸出頻率為fr/2,但在實際設計的DDS系統中,由于輸出濾波器的非理想性,一般輸出信號的最大頻率只能達到參考時鐘頻率fr的40%左右。

(1)硬件設計

系統框圖如圖2所示。

本系統采用AD公司的DDS芯片AD9832。AD9832是一塊集成了一個32位的相位累加器、正弦函數功能查詢表和一個10位D/A轉換器的CMOS芯片。它的最高時鐘頻率為25MHz,內部包含兩個32位的頻率寄存器和四個12位的相位寄存器,可以產生一個最高頻率為10MHz,頻率和相位都可以編程控制的模擬正弦波,它的頻率分辨率為0.00582Hz,相移可以是(360/4096)°的任意整數倍,易于實現靈活的高精度PSK和FSK調制。

低通濾波器相關文章:低通濾波器原理

負離子發生器相關文章:負離子發生器原理

評論