采用非對稱雙核 MCU 提高系統性能

1、背景介紹

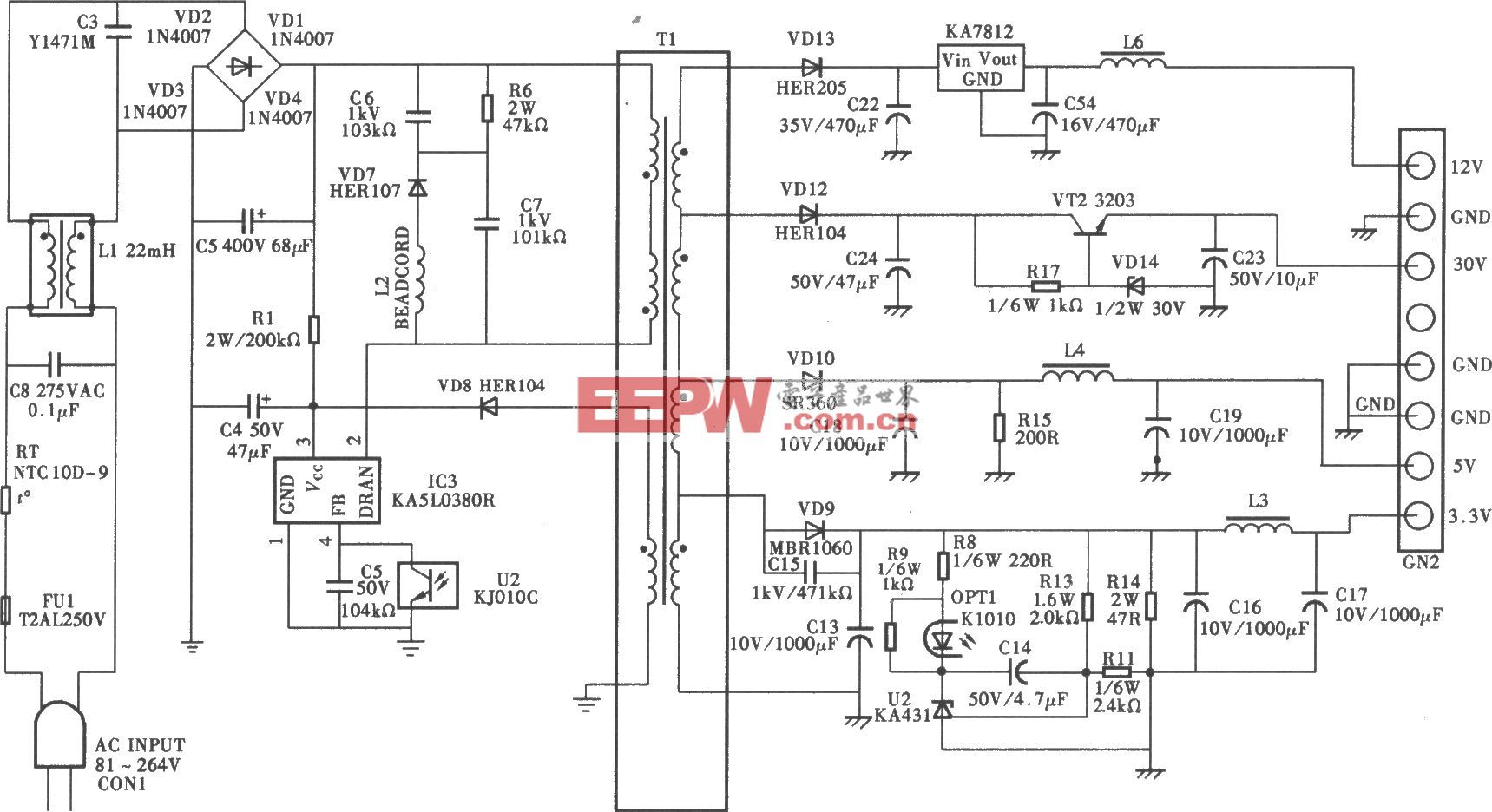

隨著各個行業朝著智能化方向的發展,嵌入式產品對能耗和效率的要求越來越苛刻。特別是在智能電網、工業和醫療等領域,一個產品的核心 MCU 處理器面臨多重挑戰。比如,一個自動化的馬達系統或者分布式工業系統,一方面需要更多的數字信號處理能力來更精確地控制馬達,另一方面也需要更多和更高級的網絡接口(CAN,Ethernet 或者 Wireless 等)來實現實時的分布式監控或控制功能。再比如圖 1,一個太陽能逆變系統,一方面需要 DSP 引擎來實現 DC/AC 或者 DC/DC 的算法,另一方面也需要將多個逆變器通過 Wireless 或者以太網 Ethernet 組成網絡,從而實現智能診斷和監控。

面對這些需求,有兩種傳統的方案可以解決。一種方案是采用兩顆單獨的 MCU/DSP,其中一顆 MCU或者 DSP 用于實現數字信號處理或者控制算法,另外一顆 MCU 實現網絡協議棧或者圖形顯示界面等。這類方案的存在諸多缺點,首先兩顆 MCU 增加了 PCB 的面積,而且雙 MCU 之間的通訊的可靠性和數據吞吐率受到限制,另外,功耗也將顯著增加,程序開發者甚至需要維護多個軟硬件開發環境。另外一種方案是采用更高主頻和更多片內資源的單核 MCU/DSP,分時地完成數據處理和輔助通信或顯示功能,這種方案顯著增加了系統成本和功耗,最致命的是,當客戶的產品需要增加新的功能的時候,工程師需要重新計算 MCU 內核的資源和不同任務所需要的運行時間,需要更多的測試時間,因此不利于擴展和產品維護。

面對種種不足,異構雙核架構應運而生,可以很好解決上述問題。事實上,非對稱雙核架構 MCU 可以將不同的系統任務分配于不同的 MCU 內核,分工精細,并且可以最佳地平衡性能、功耗和成本。兩個MCU 內核間的通信可以通過不同的方式來實現,比如分享內存區和消息區,非常簡單和易于實現。在下面的章節,本文將以 TI 最新的 Concerto 系列產品 TMS320F28M35H52C 為例,詳細闡述非對稱異構雙核 MCU 的優勢,及其為系統帶來的性能提升。

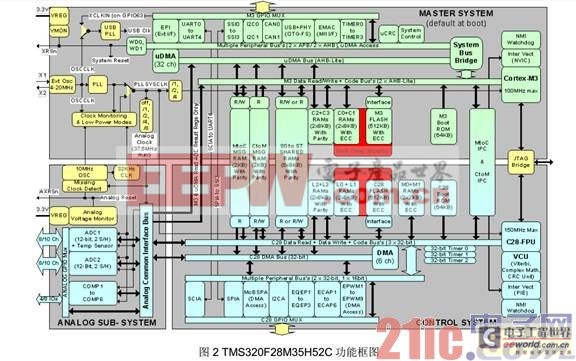

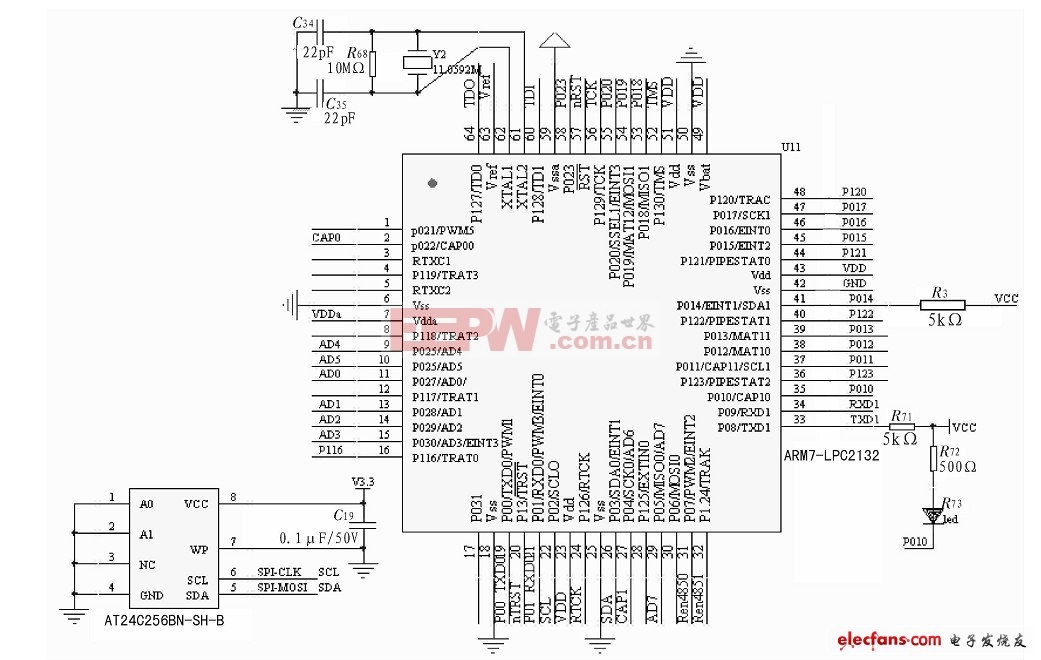

C2000 Concerto 系列 MCU 是 TI 推出的創新性的異構雙核產品。Concerto 混合架構通過將業界最好的實時控制功能和通訊功能集成在一個芯片內,提供高性能、高效率和可靠性,從而實現實時控制環路和低延時的快速通訊響應[1]。以下從內核、存儲器架構、通訊外設等方面闡述其特點。Concerto 系列 TMS320F28M35H52C 功能框圖如下圖 2 所示。

首先是高性能的內核。Concerto 系列 MCU 包含 Cortex-M3 和 C28x 兩個內核。Cortex-M3 內核是Concerto 的主系統 Master 子系統內核,主頻最高可運行于 125 MHz。Cortex-M3 內核是 32 位的ARM 核,超高的性價比,已經被業界廣泛使用,其性能和穩定性也已被用戶所廣泛接受,非常適用于通訊和事件控制。C28x 是新一代的 32 位 DSP 內核,是 TI 大多數現有的 C2000 產品的內核,最高可運行于 150 MHz,Concerto 中的 C28x 帶浮點運算單元(Floating-Point Unit),VCU 協處理器等,性能超強,非常適用于大吞吐量的數據處理。C28x 作為 Control 子系統,宏觀上受控于 Cortex-M3 Master 子系統。

其次是優化的存儲器架構。如圖 2 所示,TMS320F28M35H52C 的 C28x 可支配 512KB 帶 ECC 校驗的 Flash 存儲器,64KB ROM,36KB 帶 ECC 校驗的 RAM;Cortex-M3 可支配 512KB 帶 ECC 校驗的Flash 存儲器,64KB ROM,32KB 帶 ECC 校驗的 RAM [3]。在兩個內核之間,是共享的外設和存儲區。總共 64K 字節的共享 RAM,4K 的消息 RAM。

再次是外設。如圖 2 所示,TMS320F28M35H52C 的 C28x 內核可支配 DMA、高速 ADC(3MSPS)、多路高精度的 PWM(24 路 PWM和 16 路高精度 HRPWM)、eCAP、eQEP 等為閉環控制所優化的控制外設;Cortex-M3 內核可支配多個串行接口、以太網、CAN 等工業通訊外設。同時,兩個內核還可共享 ADC 等外設,增強整個系統的靈活性。

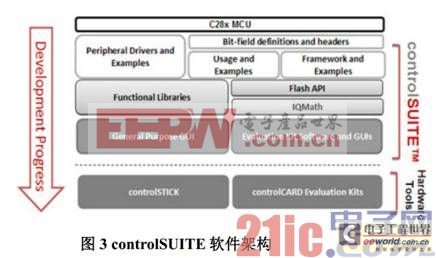

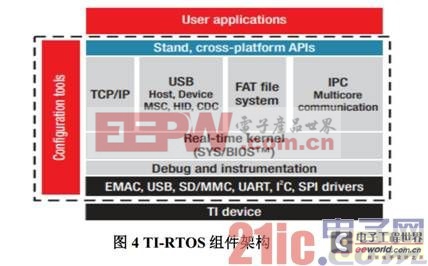

最后是軟件架構。如圖 3 所示,controlSUITE 是一個集成所有 C2000 MCU 的開發資源和軟件包和開發平臺,它為 TMS320F28M35H52C 的開發者提供了外設例程、DSP 庫、文檔、開發板資料。ControlSUITE 還提供免費的全功能實時操作系統 TI-RTOS 平臺,如圖 4 所示,TI-RTOS 是基于SYS/BIOS 實時內核,集成了穩定的中間件,例如 TCP/IP 協議棧、USB 協議棧、FAT 文件系統、IPC多核通訊組件等。

3、IPC 內核間通信

Cortex-M3 和 C28x 內核之間的通信主要完成兩大功能,一是數據通信,二是傳遞狀態和控制信息。IPC(內核間通訊)的數據通信需要較大的 RAM 來支持,而傳遞狀態和控制等信息只需要一系列狀態標志位即可。此外,Cortex-M3 側的 UART4 與 C28x 側的 SCIA;以及 Cortex-M3 側的 SSI3 與 C28x側的 SPIA 在 Concerto 內部實現互聯,不需要在芯片外部硬件連接,而是否使能這類功能則有 CortexM3 系統配置。

3.1 Message RAM 內存區

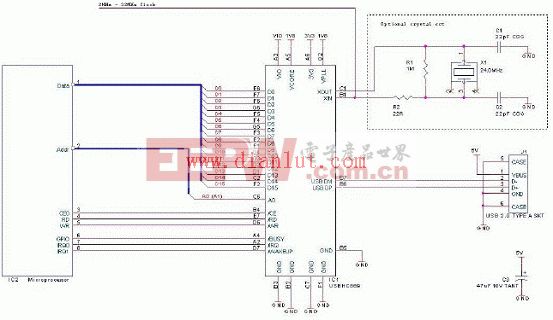

TMS320F28M35H52C 使用 Message RAM 實現 IPC 的數據通信。如圖 5 所示,2K 字節的 MTOC Message RAM 用于從 Master (Cortex-M3)子系統向 Control(C28x)子系統傳遞消息;2K 字節的CTOM Message RAM 用于從 Control 子系統向 Master 子系統傳遞消息。由于兩個子系統都配有 DMA外設,因此,DMA 也可以讀寫 Message RAM,從而提高系統效率。Message RAM 區通過 RAM 內存的讀寫權限保證了 Message 的互斥訪問,例如,C28x CPU 與 DMA 可以讀寫訪問 CTOM Message RAM 區,而 Cortex-M3 CPU 和 uDMA 只能讀訪問 CTOM Message RAM。同樣,兩個內核對于MTOC Message RAM 區的讀寫訪問權限則正好相反。

評論