IXP425和DM642的會議電視多點控制單元硬件設計

IXP425外掛一片Flash,存儲BOOT程序。芯片啟動后,從大容量Flash中導入IXP425所需映像到內存中。DSP的程序不單獨配置Flash存儲器,IXP425通過PCI總線把DSP的程序導入到各自的RAM中運行。IXP425是PCI總線的主器件,其他DSP芯片為從器件。

IXP425通過PCI總線啟動DSP的過程如下:

①DSP的配置引腳設置為PCI BOOT模式(AEA[22:21]=01,[PCI_EN:TOUT0/MAC_EN]=10)

②IXP425通過CPLD釋放DM642的復位引腳,DM642進入安裝狀態;

③IXP425通過PCI總線配置DM642的PCI寄存器;

④IXP425設置DM642的存儲器和I/O空間;

⑤IXP425把DM642的BOOT程序導入DM642內部RAM中,起始地址為0;

⑥IXP425訪問DM642的存儲器空間,把程序寫入DM642的內存中,DM642的頁寄存器(DSPP)可以使IXP425能夠訪問DM642的所有空間;

⑦IXP425置DM642的HDCR寄存器的DSPINT位為1,把DM642從安裝狀態釋放;

⑧DM642從地址0處開始運行BOOT程序。

2.3.4 OPLD設計

單板CPLD完成的具體功能如下:單板IC復位控制、中斷處理、時鐘檢測、時鐘分頻、時鐘計時(時鐘同步)、片選譯碼、I/O擴展,單板采用一片CPLD,CPLD資源要求僅能使用到70%,預留日后升級使用和防止布線緊張。

2.4 時鐘設計

(1)PCI時鐘

33 MHz晶振的輸出經過一個BUF之后分出 8路:一路給CPLD作為檢測時鐘;一路給IXP425的OSC-IN作為芯片工作時鐘;一路給IXP425的EX_CLK引腳,作為Expansion總線時鐘;一路給IXP425的PCI,作為PCI的時鐘;剩下4路送給PCI時鐘驅動器。

(2)以太網及SDRAM時鐘

50 MHz晶振作為CPLD的主時鐘,該時鐘經過2分頻后送給各路以太網芯片作為各自芯片的主時鐘,各個時鐘沒有同步要求。DM642 SDRAM時鐘由ICS512倍頻獲取,而IXP425的SDCLK_OUT驅動能力較強,直接驅動4片SDRAM工作。

2.5 單板電源設計

電源框圖如圖7所示。

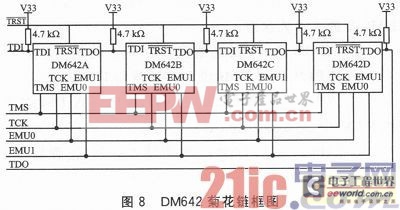

2.6 JTAG鏈接

單板CPU、CPLD的JTAG單獨成鏈,方便加載和調試,4片DM642連成一條菊花鏈,硬件兼容各個芯片單獨調試,菊花鏈框圖如圖8所示。

3 硬件調試

本多點控制單元的硬件部分主要進行以下調試:

①電源、復位模塊調試:焊接電源模塊芯片及外圍電路,測試+5 V、3.3 V、1.4 V、1.3 V電壓輸出是否正常。電壓輸出正常后,焊接復位電路元件,上電后觀察復位電壓及延續時間是否滿足設計要求,用示波器測量復位信號的電平和持續時間等是否與設計相符。上電后注意各電壓轉換芯片是否燙手,不正常則立即斷開電源進行檢查。

②最小系統調試:在板上焊接IXP425芯片、DM642芯片、CPLD、SDRAM、Flash、JTAG接口及各模塊電路外圍元件。用放大器仔細檢查有無短路、斷路、虛焊、漏焊、假焊等情況。無問題后上電,測量各芯片工作電壓是否正常,用示波器和頻率計測量各模塊的工作時鐘是否正常。利用JTAG口將硬件與計算機相連,配置好控制寄存器后,測試SDRAM讀寫功能是否正常,Flash擦寫功能是否正常。如果工作不正常,檢查時序信號、硬件連接等情況。

③PCI總線調試:測試各功能模塊之間數據傳送是否正常,如IXP425讀寫4塊DM642,D642之間讀寫數據等,需結合計算機、示波器、頻譜分析儀、邏輯分析儀等進行測試。

④網絡收發模塊調試:焊接LTX972A及外圍器件。檢測IXP425的MII接口與LTX972A芯片之間連接是否正常,通過Intel提供的LTX972A測試程序測試網絡收發模塊是否能與本地PC機通過網口進行數據通信。

4 結論

本多點控制單元在設計上具有以下特點:

①非PC機的嵌入式會議電視多點控制單元設計;

②內部采用PCI總線連接,解決會議電視多點控制單元內部突發大數據量傳輸和各數據處理模塊的同步問題;

③多并行數據處理模塊設計。

評論