理解ATE SPI (串行外設接口)

大多數Maxim? ATE設計都采用了一個串行接口,以便從外部控制器件。這種串行接口正在成為一種重要且非常有用的功能,但也可能是較難理解的部分之一。本應用筆記介紹了Maxim ATE SPI?接口,并闡述了系統架構設計方法。從時序圖可以看出如何對該接口進行編程。

串行外設接口(SPI)的基礎

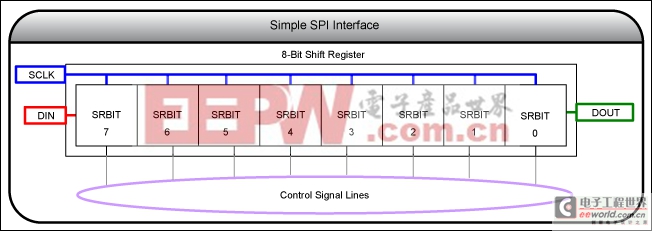

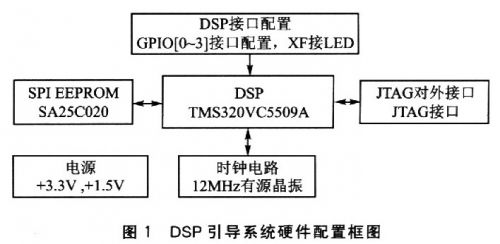

SPI是一種同步數據鏈路協議,其構想最初由Motorola?提出。按照主/從模式進行通信,其中主控設備啟動與一個或多個從設備之間的通信,在器件之間交換數據。SPI接口已經演化出了許多不同結構,但它們都采用公用的一組控制信號和輸出。最簡單的方法是基于移位寄存器的3線設計,如圖1所示。信號定義如下:

- SCLK:時鐘信號,將DIN (數據)按時序移入移位寄存器

- DIN:移入移位寄存器的數據

- DOUT:移出移位寄存器的數據

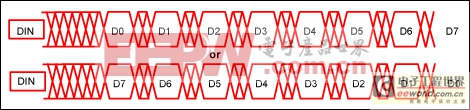

圖1. 8位SPI接口簡圖

SPI接口(圖1)的基本工作原理是將數據(DIN)移入移位寄存器,由SCLK的上升沿或下降沿控制數據移位。一旦數據移入寄存器,移位寄存器的輸出即可作為設計中的控制信號。在時鐘控制下,數據通過DOUT引腳移出,允許以菊花鏈形式連接多個接口,控制多個從器件。

Maxim ATE串行接口架構

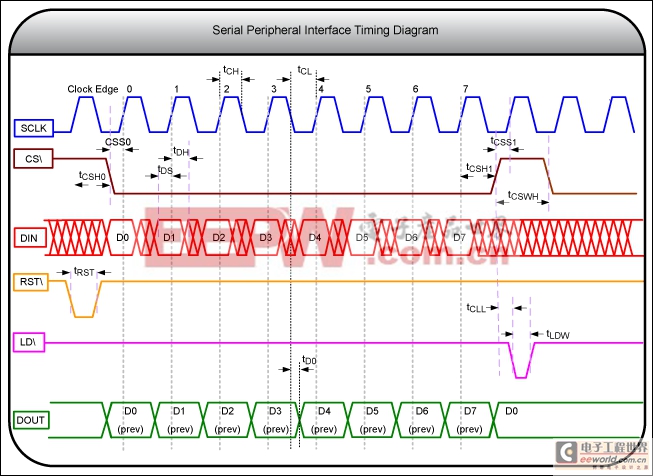

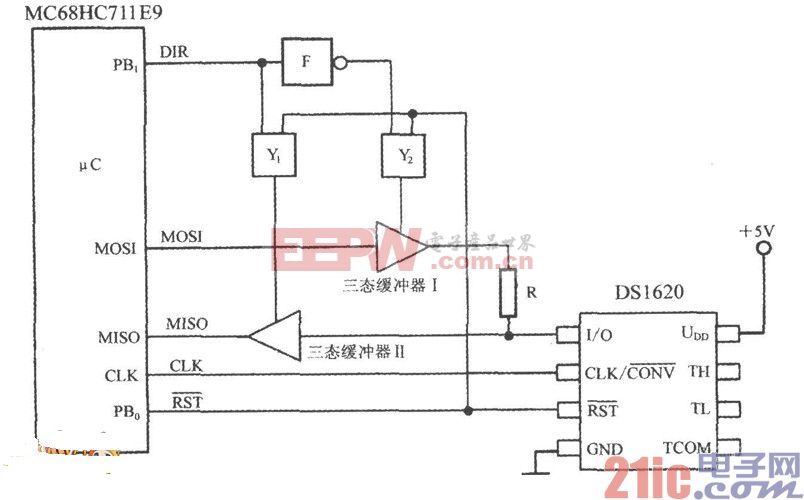

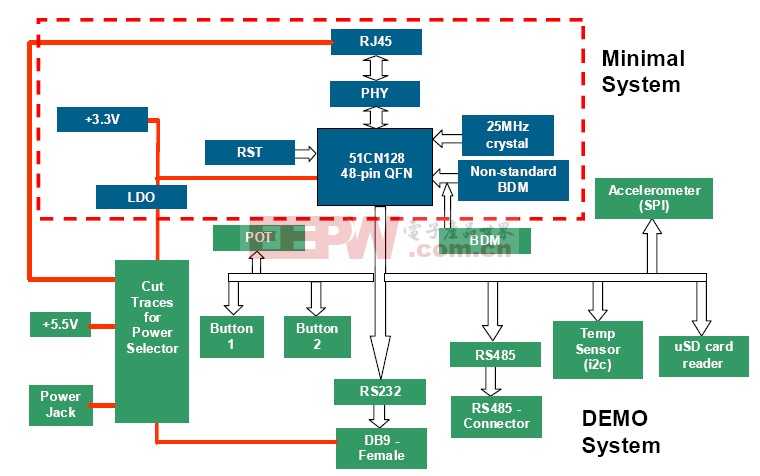

Maxim的ATE方案在圖1所示最簡方案的基礎上進行擴展,增加了另外三個信號:片選(CS*)、裝載(LD*)和復位(RST*)。另外,拓撲更改為雙緩存結構。緩存1代表增加的第一級鎖存器;緩存2代表第二級鎖存器。這種雙緩存結構能夠在兩級之間靈活地傳遞和鎖存數據。我們將探討這種架構的實現和時序圖(分別參見圖2和圖3),說明單通道、8位字SPI的工作原理。

單元和信號

8位移位寄存器

圖2所示為標準移位寄存器,它具有8個寄存器位(SRBIT0至SRBIT7)。數據(DIN)在SCLK的上升沿移入,移入所有8位數據需要8個時鐘信號。數據在第8個時鐘周期的下降沿移出(DOUT)。CS也是移位寄存器單元的一個輸入。

控制信號譯碼

控制信號譯碼電路是一個用戶邏輯單元,對SCLK、CS以及數據字中的控制位進行譯碼,使得第1級鎖存器可以保持數據或將數據傳遞至第2級鎖存器。該單元可以設計控制多路第1級鎖存器,MAX9979數據資料給出了一個示例,其中第1級輸入寄存器和通道選擇寄存器都由用戶邏輯單元控制。該8位示例中沒有控制位,移位寄存器的所有8位傳遞至第1級鎖存器。

8位鎖存器

提供兩級或兩組完全相同的鎖存器。該示例采用8位鎖存器(SRBIT0至SRBIT7)。鎖存器為透明傳輸,在鎖存時鐘輸入的下降沿將輸入數據傳遞至輸出。鎖存器輸出在鎖存時鐘的上升沿保持或鎖存數據。輸出保持鎖存狀態,直到鎖存器時鐘輸入變為低電平。第1級鎖存器的時鐘信號為SCLK、CS和控制位的譯碼信號。第2級鎖存器的時鐘信號為LD信號。

控制信號線

控制信號線為第2級鎖存器輸出。它們作為數字控制信號控制器件的內部功能或工作模式。

“低電平有效”

信號CS、LD和RST為“低電平有效”控制信號。“低電平有效”表示信號只有為邏輯低電平時才有效。

圖2. 8位字、雙緩存SPI接口的簡單示例

圖3. 8位字SPI示例的詳細時序圖

工作原理

下文所示時序對應于圖2和圖3所示的SPI示例。該設計中,選擇在時鐘的上升沿將信號移入器件,也可以使用下降沿。數據按照從MSB (最高有效位)至LSB (最低有效位)的順序移入,也可以從LSB至MSB移入,如本應用所示。

- 在SCLK的上升沿將數據移入移位寄存器。

- DIN數據經過8?個時鐘周期后,在SCLK的下降沿從接口(通過DOUT)移出。

- CS由SCLK觸發控制。在低電平有效的CS下降沿將數據傳遞至第1級鎖存器,并在CS的上升沿鎖存至第1級。如果CS保持為高電平,數據僅傳送至DOUT,不會出現在第1級鎖存器。

- 與LD控制信號異步加載第2級鎖存器。如果LD保持為邏輯高電平,則第1級緩存輸出不會傳遞到第2級緩存輸出。若LD保持為低電平,第1級緩存輸出將直接通過第2級鎖存器。在LD控制信號的上升沿鎖存第2級輸出。

- RST將把串行接口控制信號復位到默認狀態。

- 圖3所示為所有串行接口輸入、輸出的詳細時序。

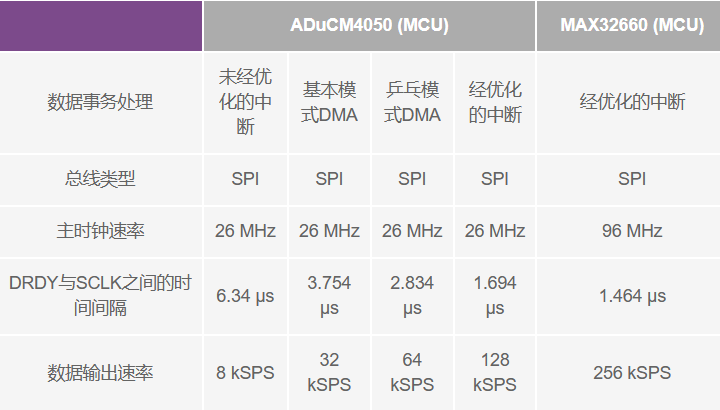

SPI接口只有符合具體的時序指標要求才能正常工作。這些指標在器件數據資料中列出。表1定義了圖3相應的技術指標,并給出了一些典型值以供參考。

表1. SPI時序要求、定義及典型值

| Specifications | |||||

| Parameter | Symbol | Min | Typ | Max | Units |

| Serial clock frequency | fSCLK | — | — | 50 | MHz |

| SCLK pulse width high | tCH | 12 | — | — | ns |

| SCLK pulse width low | tCL | 12 | — | — | ns |

| SCLK fall to DOUTvalid | tDO | — | — | 22 | ns |

| CS-bar low to SCLK high setup | tCSS0 | 10 | — | — | ns |

| SCLK high to CS-bar high hold | tCSH1 | 22 | — | — | ns |

| SCLK high to CS-bar low hold | tCSH0 | 0 | — | — | ns |

| CS-bar high to SCLK high setup | tCSS1 | 5 | — | — | ns |

| DIN to SCLK high setup | tDS | 10 | — | — | ns |

| DIN to SCLK high hold | tDH | 0 | — | — | ns |

| CS-bar pulse width high | tCSWH | 10 | — | — | ns |

| CS-bar high to LD-bar low setup | tCLL | 22 | — | — | ns |

| LD-bar pulse width low | tLDW | 20 | — | — | ns |

| RST-bar low pulse width | tRST | 10 | — | — | ns |

SPI接口的主/從配置

有三種方法實現主/從配置:

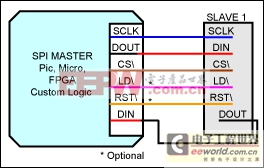

- 一主一從,如圖4所示。

- 一主多從,采用菊花鏈拓撲結構,如圖5所示。

該方法的優勢在于:- 主器件僅需要一個片選引腳。

- 以菊花鏈形式將DOUT引腳連接至下一個從器件的DIN;最后一個從器件的DOUT返回至主器件DIN端口進行讀取。

- 每個從器件沒有獨立控制信號。

- DATA字較長。

- 由于必須在觸發片選信號之前更新所有從器件,所以更新速度較慢。

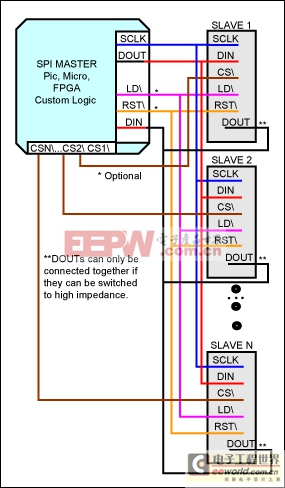

- 一主多從,每片從器件都有其各自的片選引腳,如圖6所示。

該方法的優勢在于:- 每個從器件均可獨立控制。

- 工作速率較快。

- 主器件需要更多的I/O控制引腳。

- 如果DOUT不能處于高阻態,則不能回讀數據。

圖4. 單個主/從SPI接口

圖5. 一主多從—菊花鏈結構,一個片選信號控制所有從器件。

圖6. 一主多從—每個從器件都有獨立的片選信號。

常見的SPI錯誤

根據數據資料確定數據是在時鐘的正向上升沿還是負向下降沿移入。請注意不要混淆具有不同時鐘沿要求的從器件。如果存在不同的時鐘要求,請務必在軟件或硬件中完成正確的轉換。

根據數據資料確定是MSB在前還是LSB在前移入數據。

確保CS在相對于時鐘沿的數據字附近正確控制。

如果字長不是8位或單字節的倍數,請務必在字開頭或結尾處添加零,以確保以字節的整數倍移入。有些控制器或主器件,一次只能輸出1個字節。如果是這種情況,需確保不會將實際數據從從器件中移出。若要控制指定從器件,需確保從器件擁有完整數據。

請不要將多個DOUT連接在一起,除非它們具有高阻態選項。

請仔細閱讀數據資料,確定已經理解、掌握從器件的使用細節。“字”可以包含數據、地址和控制位。

請注意,以菊花鏈連接多個器件可能導致更新速度緩慢。

SCLK信號為高速信號并送至多個位置。確保該信號經過適當緩沖以驅動多個電路,從而避免時序誤差。所有驅動多個電路的信號都應該具有足夠的驅動能力。

總結

從6個基本信號的角度介紹了Maxim ATE SPI串行接口的基本工作原理和時序,它們分別為:SCLK、CS、DIN、RST、LD和DOUT。RST和LD可選。即使不同電路之間的結構會有所調整,但這6個信號的時序定義了SPI接口的外部工作特性。本文結合6個基本信號,以8位字、雙緩存接口為例介紹了SPI的工作原理。該接口是Maxim ATE產品遵循的拓撲結構。查看每個器件的數據資料可以了解不同接口的差異和增強功能,但所有接口都遵循本文所述時序。充分理解本文給出的示例有助于您解讀、理解Maxim的許多ATE串行接口。

*注:后綴“” (例如:CS、LD、RST)表示這些引腳為低電平有效。

評論