高頻四象限電流乘法器電路設計

本文提出了一種高頻四象限電流乘法器。該乘法器電路結構對稱。提出的乘法器電路工作在±1.18 V的電源電壓下。由于從輸人端到地的低寄生電容,該電路可以工作在高頻條件下,實驗測得它的-3 dB帶寬可以達到1.741GHz。

1 電路工作原理

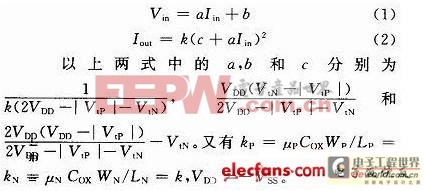

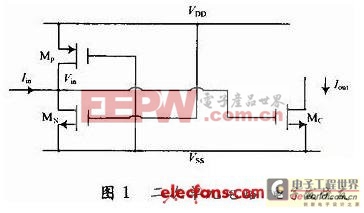

本文提出的這種電流乘法器是基于圖1所示的基本的單元電路而設計成的。圖1所示的電路,輸出電流Iout和輸入電流Iin是二次函數的關系。這種二次單元電路是由MN、MP和MC組成的。其中MN和MP是偏置工作在三極管區,MC是工作在飽和區。如果MN和MP有相同的跨導因子(kP=μPCOXWP/LP=kN=μNCOXWN/LN=k),從圖1可以很容易得到輸入電壓Vin和輸出電流的Iout的表達式如下:

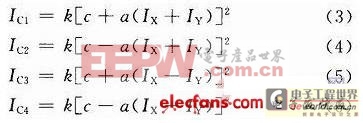

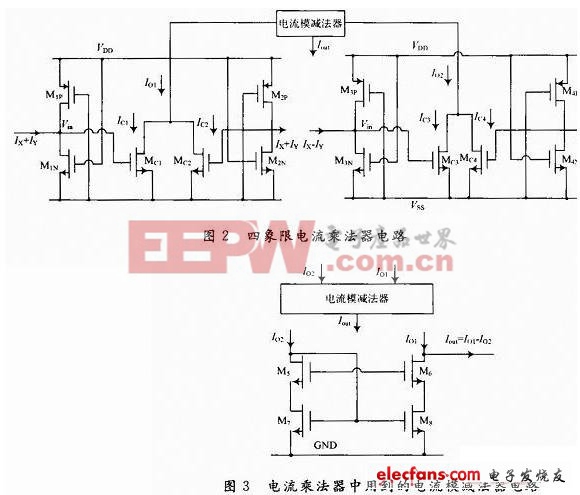

很顯然,二次單元電路帶來了輸出電流和MOS管漏極電流的二次函數的關系。在圖2中顯示了提出的四象限電流乘法器電路。圖2中用到的電流模減法器電路如圖3所示。這里用到的減法器不同于文獻中的電壓減法電路。圖2電路是由4個二次單元電路構成。該乘法器的輸入電流是輸入電流IX和IY的和與差。通過使用由式(2)所得到的輸出電流和輸入電流的二次關系,可以得到MOS管MC1,MC2,MC3和MC4的漏極電流的表達式如下:

從圖2可以看出,由于IO1是IC1和IC2的和,而IO2是IC3和IC4的和,因此可以推導出IO1和IO2表達式如下:

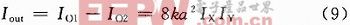

這種四象限乘法器的輸出電流Iout是IO1和IO2的差,由如下表達式給出:

可以看到在公式(9)中,輸出電流IOUT等于電流IX和IY的乘積,伴有一個由跨導因子K和依賴于電源的參數a決定的乘法增益因子。很顯然,可以通過調節跨導參數k和參數a,來調節乘法器的增益。參數k和MOS管的尺寸直接相關。減小跨導參數k或MOS管的尺寸,帶來了較高的增益和較低的功耗,同時由于與MOS管相關的較小的寄生電容的作用,使得電路的速度也改進了。但是,減小參數k,仍需慎重考慮。因為較小的跨導參數k會帶來較低的線性度和較小的靜態電流,而這會降低輸入電流的范圍。相反,大的參數值k會帶來較大的靜態電流,因此會有較大的電流輸入范圍。但是這就會增加電路的總功耗。顯然,參數k的選擇要求最佳化。當然,也可以通過調節電源依賴因子a來調節調節電路的增益。a的大小直接決定了電路的功耗和輸人工作電流的范圍。

2 電路仿真結果

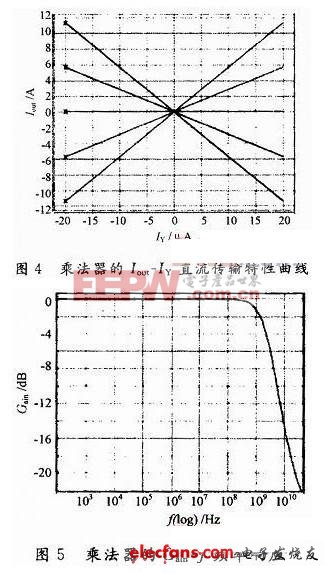

對圖2所示乘法器的性能使用Hspice仿真軟件進行仿真驗證,其中MOS晶體管模型參數由標準的0.35μm CMOS工藝提供。所有NMOS管和PMOS管的閾值電壓分別為0.53~0.69 V。MOS管的寬長比設置如下:M1P~M4P,60μm/0.7μm,MIN~M4N,20μm/0.7μm,MC1~MC4,25μm/0.7μm,M5~M8,25μm/0.7μm。電源電壓為±1.18 V。圖4顯示了電流乘法器電路在輸入電流IY在-20~20 μA范圍內變化時的直流傳輸特性曲線。在圖4中,從右下到右上的5條曲線分別是輸入電流IX為-20μA,-10μA,0μA,10μA和20μA時的輸出電流Iout隨輸入電流IY變化的直流傳輸特性曲線。

圖5顯示了提出的乘法器電路的頻率響應曲線。在仿真過程中,輸入電流IX為正弦信號電流,同時輸入電流IY保持為10μA。由圖5可以看到,電路的電流標準分貝增益隨頻率變化,所設計的乘法器電路展示出了良好的頻率特性,得到的-3 dB帶寬為1.741 GHz,遠遠超過了文獻中提到的(413MHz)。這是由于電路中從輸入端到地的寄生電容減小的緣故。整個電路的功耗為1.18mW。

3 結語

本文提出了一種低壓高頻四象限電流乘法器電路。該乘法器電路的優點是電路結構簡單而且對稱。電路可以工作在高頻條件下(f-3dB= 1.741 GHz),整個電路的功耗為1.18mW。

評論