頻譜儀多種內核通信機制的方案設計

多核體系結構為性能提高和節能計算等領域開辟了新的方向。核與核之間的連接方式、通信協調方式等都是研究重點。本課題的研究基于手持式頻譜分析儀系統平臺,該系統采用的是ARM、DSP、FPGA的三核架構。各核心分別完成不同的任務,然后核心間進行參數發送、數據交換,實現系統功能。設計重點是解決核心間的通信問題。

1 ARM與DSP、FPGA通信的硬件設計

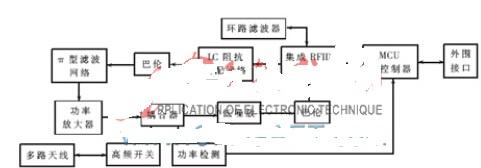

手持式頻譜儀中頻信號處理板主要包括4個部分:模數轉換器(AD9244)、FPGA(XS3C5000)、DSP(TMS320C6412)、ARM(AT91RM9200)。ARM在手持式頻譜儀中的位置和作用如圖1所示。

ARM的硬件設計參考Atmel公司提供的評估板資料。主要包括以下幾個單元電路的設計:電源電路、時鐘電路、復位電路、啟動模式選擇電路、JTAG接口電路、Debug串口電路、外部擴展SDRAM電路、外部擴展NOR Flash(AM29LV320DB)電路、與DSP通信的HPI接口電路、與FPGA通信的SPI接口電路、連接溫度傳感器的I2C接口電路、以太網接口電路。

1.1 HPI接口電路設計

ARM與DSP的HPI總線采用16位數據通信,而且HPI總線是數據和

評論