USB接口芯片FT245BM的功能及其應用

通用串行總線USB(Universal Serial Bus)由于具有數據傳輸速率高、易于使用、支持熱插拔等特點,越來越成為一種流行的計算機通信接口。FT245BM芯片是由FTDI(Future Technology Devices Intl. Ltd)公司推出的第二代USB接口芯片,與其他USB芯片相比,應用FT245BM芯片進行USB外設開發,只需熟悉單片機(MCU)編程及簡單的VC或VB 編程,而無需考慮固件設計以及驅動程序的編寫,從而能大大縮短USB外設產品的開發周期。此外,FT245BM支持USB1.1及USB2.0規范,數據傳輸速度可達到1M byte/s。因此,FT245BM是開發USB外設所需接口芯片的極佳選擇。

FT245BM的結構與功能

FT245BM芯片是一種32腳,LQFP封裝的芯片,管腳定義如下:

D[0-7](25,24,23,22,21,20,19,18):雙向數據信號線;

RD#(16):讀信號;

WR(15):寫信號;

TXE#(14): FIFO發送緩沖區空標志信號;

RXF#(12): FIFO接收緩沖區非空標志信號;

USBDP(7),USBDM(8):USB數據信號正端,USB數據信號負端;

EECS(32),EESK(1),EEDATA(2):EEPROM片選線,時鐘線,數據線;

PWREN(10):電源使能信號;

SI/MU(11):立即發送或喚醒信號;

RESET(4):復位信號;

RSTOUT(5):內部復位生成器的輸出信號; XTIN(27),XTOUT(28):時鐘輸入信號,輸出信號;

TEST(31):測試信號;

3V3OUT(6):3.3V輸出信號;

VCC(3,26),VCCIO(13),AVCC(30):芯片電源,控制引腳電源,內部模擬電源;

GND(9,17),AGND(29):芯片地,內部模擬地。

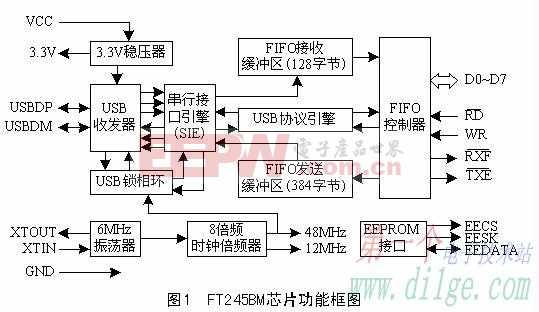

芯片內部由3.3V穩壓器,USB收發器,鎖相環,串行接口引擎(SIE),FIFO控制器,USB協議引擎,FIFO接收緩沖區,發送緩沖區以及6M振蕩器,8倍頻時鐘倍頻器等組成。

FT245BM芯片可實現USB接口與并行I/O接口之間數據的雙向轉換。一方面,當USB收發器從主機接收USB串行數據后,由串行接口引擎將數據轉換成并行數據,存儲在FIFO接收緩沖區, FIFO控制器檢測到讀信號RD為低,就把接收緩沖區的數據送到并行數據線D0-D7上;另一方面當FIFO控制器檢測到寫信號WR為高時,就從數據線D0-D7上讀取并行數據,存儲在FIFO發送緩沖區,并行數據經串行接口引擎轉換成USB串行數據,再通過USB收發器傳送到主機。可見FT245BM芯片自身就可完成數據轉換,而不需要設計者考慮硬件設計。其內部結構功能如圖1。

圖1 FT245BM芯片功能框圖 |

硬件接口設計

接口電路原理圖見圖2。

設計采用USB總線供電,圖2中FT245BM與一片MCU相連,MCU的一個8位端口用來傳輸數據,另外一個端口用來控制和產生FT245BM需要的4根握手信號線,即RXF#、TXE#、RD#、WR。TXE#為低,表示當前FIFO發送緩沖區空,這時WR脈沖由高變低就將數據線D0-D7上數據寫入FIFO發送緩沖區中;當TXE#變高時,表示當前FIFO發送緩沖區滿或者正在存儲上一個字節,禁止向發送緩沖區中寫數據。RXF#為低,表示當前FIFO接收緩沖區有數據,這時RD#脈沖由低變高,將從FIFO接收緩沖區中讀取數據;讀信號RD#為低時,把數據讀到數據線D0...D7上;當RXF#為高時,禁止從FIFO接收緩沖區讀數據

評論