DS1820單總線(1-wire)數字溫度傳感器

(7)讀暫存存儲器的溫度數據。

2 控制器設計

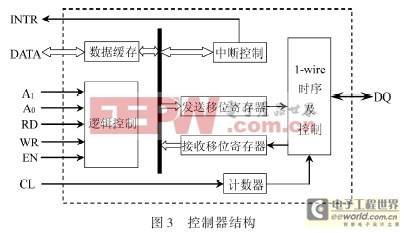

2.1 控制器結構

控制器結構如圖3所示,控制器由4部分組成,即邏輯控制、單總線時序控制、數據緩存和計數器。邏輯控制部分用于實現與CPU的通信,D0~D7為8位雙向數據線,EN為啟動信號,下降沿有效。A1、A0為地址信號,其組合決定控制器的工作狀態。A1A0=00,控制器對DS1820執行復位操作;A1A0=01,控制器執行寫入操作;A1A0=10,控制器執行讀出操作。控制器由外部提供200 kHz的時鐘信號CLK,產生5 μs的計數周期,控制器以5 μs為一個時間片形成DS1820的讀寫時序。計數器的計數輸出值控制讀寫周期。單總線時序控制部分的主要功能是產生單總線的讀寫時序,并向DS1820輸出控制命令,讀出DS1820測得的數字溫度值及其他輸出信息。

2.2 讀寫時序的實現

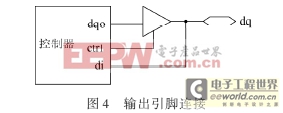

DS1820要求引腳驅動必須是漏極開路引腳,控制器用三態門與DS1820連接,如圖4所示。其中ctrl為三態門控制信號,當ctrl=0時輸出信號,ctrl=1時輸入信號。控制器采用5 μs作為基本計時單位,可以保證DS1820時序關系有一定的余地。

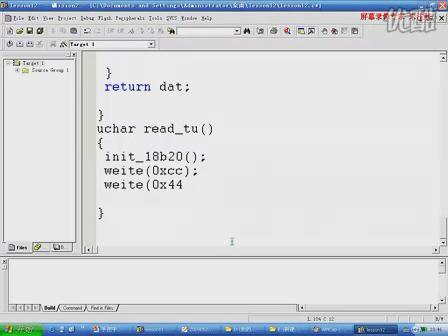

寫字節部分VHDL代碼:

PROCESS(cq)—輸出1 bit

SIGNAL cout:STD_LOGIC_VECTOR(2 DOWNTO 0);

VARIABLE di:STD_LOGIC;

BEGIN

ctrl=‘0’;

IF(cq>=“0000” AND cq=“0010”)THEN

di:=‘0’;——拉低輸出電位10 ms

ELSIF(cq>“0010”AND cq“1110”)THEN

di:=rq; ——取發送移位寄存器的輸出位

ELSIF(cq>=“1110”)THEN

di:=‘1’;cout=cout + 1;

END IF;

dqo=di;

END PROCESS;

評論