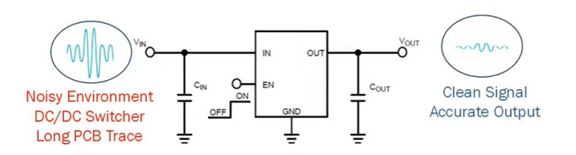

單電源供電的全差分斬波運放電路

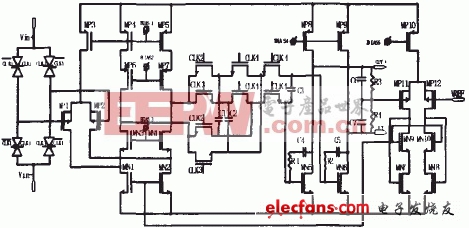

圖2 斬波運放的電路結構

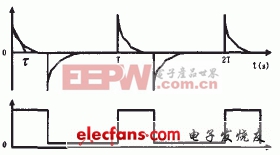

輸入斬波開關完成對音頻信號的調制作用,斬波開關在時鐘上沿和下沿都會引入殘余電壓失調,圖3為零輸入時殘余失調電壓的波形。

圖3(a)殘余失調電壓(b)斬波信號

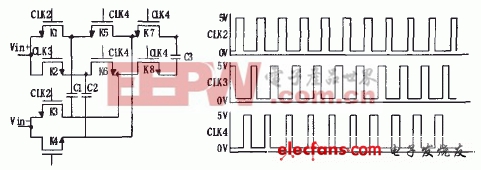

圖4 T/H解調及控制時序

通過對CMOS開關特性分析可以得出等效輸入殘余失調電壓為Vos,rmts=2Vspiketfch,其中t是MOS開關的時間常數,從此式可以看出消除殘余電壓失調有三種方法:

1.降低斬波頻率:

2.減小輸入電阻;

3.減小斬波開關的電荷注入效應。

由于MOS管1/f噪聲的拐角頻率一般都在幾十KHz以上,減小斬波頻率不能很好地對1/f噪聲進行調制,而輸入電阻只與信號源內阻有關,在設計中很難將輸入電阻降低,因此只能考慮減小開關的電荷注入效應。為此輸入斬波開關采用互補時鐘結構,在尺寸上使用最小線寬,一方面能夠減小傳輸的導通電阻,提供較大的電壓擺幅;另一方面減小了電荷注入和饋通的影響,降低了殘余電壓失調。考慮到PMOS管比NMOS管的1/f噪聲特性好,所以輸入管MP1和MP2采用大面積的PMOS管,既能減小因器件的失配引起的電壓失調,又可以降低晶體管1/f噪聲的拐角頻率,改善運放的噪聲特性。

為了更小地降低殘余電壓失調,fold—cascode運放的輸出采用T/H解調技術,電路結構和時序如圖4。該電路的工作原理:在跟蹤信號時K1~K4閉合,K5~K8斷開,輸出信號保持在電容C1和C2上,當電

電荷放大器相關文章:電荷放大器原理

評論