解讀SAR ADC驅動運算放大器選擇

運算放大器的軌至軌運行是指其輸入級或輸出級,或者是指其輸入級和輸出級。作為驅動 SAR ADC 輸入端的一個緩沖器,我們更關注的是運算放大器軌至軌的輸出能力。一般說來,該輸出能力表明了輸出級能夠接近電源軌的程度。該參數可在大多數低頻或 DC 輸出信號產品說明書中找到,因此更好地了解輸出擺幅能力,將有助于在既定條件下驅動 ADC 輸入端時,確定最佳工作點。

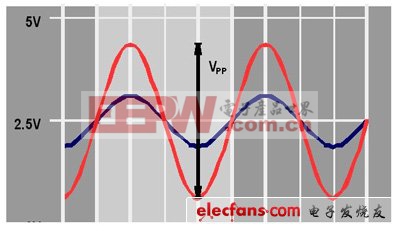

為了確定輸出級極限,應事先開展如下測量工作:對于電源電壓為 5V 的軌至軌運算放大器來說,輸入信號的偏移為 2.5V 或為電源電壓的一半。該運算放大器應事先在電壓跟隨器(或增益為 +1)配置中予以設置。峰至峰輸入 AC 信號振幅從0 提高到了 5V,達到了電源電壓電平。當輸出級達到其極限時,則可以顯示出不同的峰至峰輸出電壓在運算放大器輸出端的總諧波失真與噪聲 (THD+N) 的測量情況(請參閱圖 1)。

圖 1:測量得出的運算放大器輸出信號

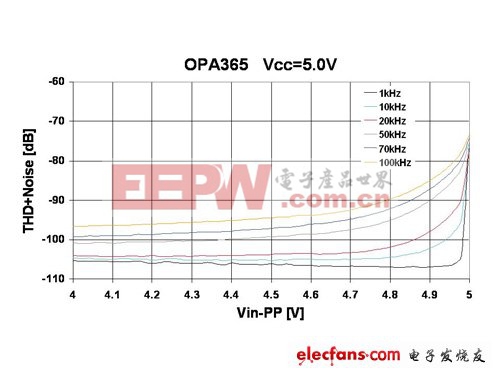

通常情況下,當信號振幅增大時,低頻信號 (1kHz)、總諧波失真保持不變。只有當輸出電壓和電源軌之間的差值低于 10mV 時,才會導致性能顯著下降。而當輸出信號頻率增加時,輸出電壓和電源電壓之間的差值也會隨之增大。對于 10kHz 的信號而言,當上述電壓差值低于 200mV時,相關性能才開始下降;對于 20kHz 的信號而言,當上述電壓差值低于 300mV 時,相關性能才開始下降;以此類推。如果要保持相關性能不變,當頻率增大時,則可減小輸出信號的擺幅。如欲了解有關的測量結果,敬請參閱圖 2。

圖2:在不同的輸出信號情況下,測量得出的運算放大器失真

考慮到運算放大器的輸出級極限,這些測量結果將有助于我們確定 SAR ADC 電路的最佳工作點。正如在上述例子中,采用電源電壓為 5V 的 OPA365,在頻率為 150kHz,輸出信號高達 4.1VPP 時,仍能保持相關的性能不變。由于電源軌留有 450mV 的裕度,所以在 100kHz 的范圍內 OPA365 能輕而易舉的驅動信號。

RC 負載對運算放大器的影響

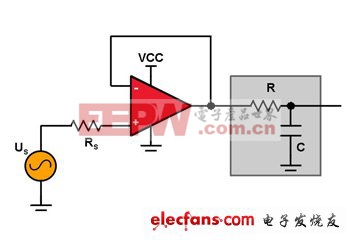

以前,我們曾證實,對于最佳的 AC 性能而言,運算放大器的輸出信號擺幅將會介于 450mV 和 4.55V 之間。用于驅動 SAR ADC 運算放大器的第二個重要參數就是要找出其驅動不同的 RC 負載的極限。為此,我們大力推薦在 ADC 輸入端采用 RC 濾波器來限制輸入噪聲的帶寬,并幫助運算放大器驅動由 SAR ADC 產生的開關電容負載。圖 3 表明了測試調整電路 (test setup circuit) 如何幫助我們確定具有 RC 負載的運算放大器的驅動極限。

圖 3:測量運算放大器驅動 RC 負載的能力

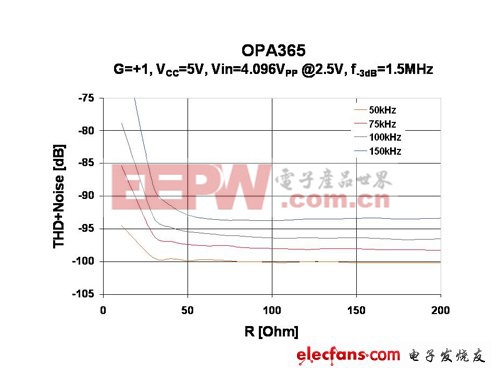

首先,將 RC 電路的截止頻率定為 1.5MHz。這一頻率限額是以在未來設計中將要采用的 ADC 預期采集時間為基礎設定的。另外,如欲保持截止頻率不變,則應開展不同 RC 組合以及不同信號頻率的測量工作(請參閱圖 4)。

圖4:在不同的 RC 情況下,測量得出的運算放大器失真情況

對于較低的頻率而言,我們則使用較小阻值的電阻或較大容量的電容器。當信號頻率增大時,阻值較大的電阻應與容量較小的電容器配合使用,以保持相關性能的穩定。對于在既定條件下的 OPA365 來說,我們發現,通過采用阻值為 50-100Ω 的電阻來改善性能并不令人滿意——尤其是對于更高的信號頻率而言,想通過采用阻值為 50-100Ω 的電阻來改善性能更是無濟于事。對于應用頻率 (applied frequency) 而言,我們可以采用阻值大于 100Ω 的電阻或容量小于 1nF 的電容器來保持 AC 性能的穩定。當選擇電阻的阻值和電容器的容量時,我們應遵循運算放大器的穩定性要求。

ADC 輸入的非線性特性

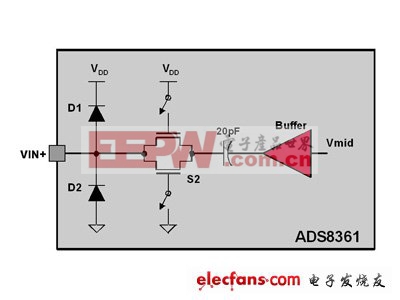

減小輸出電壓擺幅將有助于保持運算放大器的性能,但還應考慮信號的完整性及其對不同系統組件的影響。隨后可向 ADC 輸入端發送一個信號。圖 5 為常見的SAR ADC 輸入級。在流經輸入靜電放電 (ESD) 保護二極管之后,則可對一個采樣電容器和兩個場效應晶體管 (FET) 開關中的信號進行采樣。如果采用了理想的組件,本設計不會對采樣階段的運算放大器的驅動產生任何影響。

圖 5:SAR ADC 的輸入級

遺憾的是,這些組件并非理想的解決方案(請參閱圖 6),特別是臨近電源軌的等效負載非線性特性,向緩沖電路提出了新的挑戰。

圖 6:SAR ADC 的運算放大器等效負載

減小從運算放大器至 ADC 輸入端的信號擺幅,將帶來諸多益處。在運算放大器的輸出端應用 5VPP的信號將減弱總諧波失真 (THD) ,尤其是當頻率較高時,更是如此。另外,在 SAR ADC 的輸入端應用 5VPP 的信號時,要求運算放大器擁有強大的驅動能力,特別是在接近電源電壓的情況下,尤為如此。以 2.5V 的偏移量,將信號電平從 5VPP 減小到 4.1VPP,將同時為正、負電源軌增加 450mV 的裕度。這種設置使運算放大器更易于在較高頻率的情況下,提供令人滿意的 THD。目前,ADC 等效輸入負載處于線性區域,從而使運算放大器更易于為采樣電容器充電。

需要考慮的另一個問題是:ADC 的滿量程衰減。在常見的 ADC 產品說明書中可以發現,轉換器的額定電源電壓為 5V,其額定滿量程 (FSR) 為一個 5VPP 的信號。請務必注意,ADC 的輸入 FSR 取決于應用參考電壓,您可以針對新的運行條件,對 FSR 進行調整。當使用的參考電壓為 2.5V 時,對于德州儀器 (TI) ADS8361 而言,在 2.5V 或 5VPP 時 FSR 輸入信號將為 ±2.5V。將參考電壓調整為 2.048V 后,在 2.5V 或 4.1VPP 時,新的(調整后的)FSR 輸入信號將為 ±2.048V。現在,在 4.1VPP 的輸入信號中,我們就擁有了一個全 16 位的轉換功能,而無需衰減動態范圍。

采集時間與吞吐率 (Throughput Rate) 之間的關系

當選擇 ADC 時,其中最重要的參數就是速度或吞吐率。這一參數是采集(采樣)時間和轉換時間的組合。而轉換時間是轉換器設計和用以實現轉換器功能的硅處理技術綜合作用的結果。當轉換時間的縮短超過產品說明書中規定的限額時,將嚴重影響 ADC 的性能。轉換時間通常是因所采用的最大外部時鐘的不同而不同的。另外,根據產品說明書中的有關說明,上佳的系統設計實踐可將外部時鐘保持在限額之內或將轉換時間盡量縮短。另一方面,一般說來,延長轉換時間并不能改善相關性能。

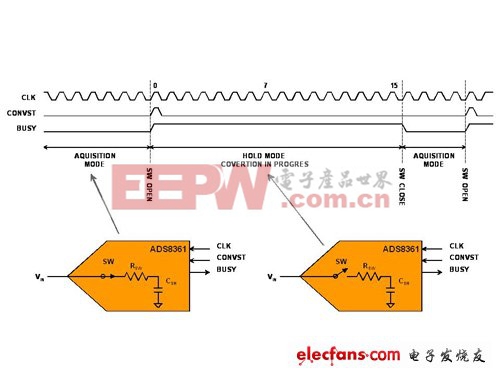

采集時間在 ADC 產品說明書中也作了明確的規定,采集時間決定著為采樣電容器充電的快慢,以達到規定的吞吐率。在采集時間臨近結束時,輸入采樣開關開啟,轉換過程隨即開始。在轉換周期即將結束時,從 ADC 所獲得的數據等同于轉換周期開始時(或采集周期結束時)采樣電容器上的電壓。請參閱圖 7。

不論 ADC 性能表現的如何卓越,如果沒有足夠的時間對采樣電容器進行全面的充電,那么轉換結果將會出現與實際模擬輸入信號不相符的情況。為了在系統設計期間控制上述參數,有兩種方法可供選擇:1)采用輸出阻抗低、運行速度快的運算放大器,或 2)在 ADC 模擬輸入端采用高截止頻率的 RC 濾波器。這種方法可導致運算放大器穩定性方面的問題,同時會給輸入模擬緩沖電路帶來較大的噪聲影響。或者,您也可以通過使用運行速度適中的運算放大器和較低截止頻率的 RC 濾波器,來延長轉換器的采集時間。

圖 7:ADC 采集和轉換周期

ADS8361 的吞吐率為 500 kSPS,最高的外部時鐘頻率為 10MHz。轉換過程分為 16 個時鐘周期,或需要 1.6μs 才能完成。其中只有 0.4μs 用于模擬輸入信號采集過程。在滿

評論