基于單片機和CPLD的PLC背板總線協議接口芯片設計(二)

3.2 基于Verilog HDL 語言的硬件程序設計

本設計采用Verilog HDL 語言進行協議芯片的程序設計,Verilog HDL 語言是一種硬件描述語言,設計數字芯片時可以按照層次描述,并可以進行時序建模。本設計采用混合設計模式,主要設計的模塊有狀態機、協議幀檢測、FIFO 控制器設計等。

1)狀態機設計。

協議芯片的頂層模塊是狀態控制器部分,協議芯片共有四個狀態, 分別處理基于Verilog HDL 程序語言的狀態機描述偽代碼如下:

2)協議幀檢測。

本協議芯片的幀校驗和采用簡單的加和形式進行,在接收一方,如果數據幀中有用數據的加和同后續的校驗和字節相同,則協議是正確的,否則丟棄該幀。協議幀校驗和計算的代碼如下:

3)FIFO 設計。

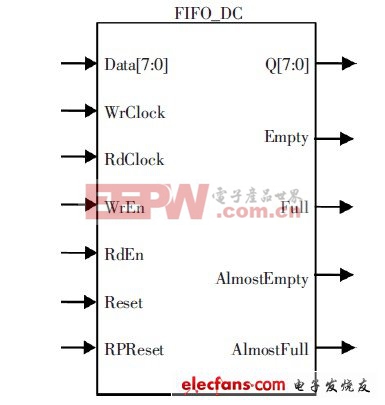

FIFO 利用了MachXO 系列CPLD 的嵌入式SRAM 塊的資源,Lattice 公司的ispLEVER 7.0 軟件提供了可配置的IP 軟核,該軟核可以采用基于嵌入式SRAM 塊實現, 也可以使用查找表實現,FIFO 的IP 核框圖如圖4 所示,FIFO 的可配置參數包括FIFO字節深度、EmptyFull、Almostempty 和AlmostFull觸發字節深度、數據寬度、大小端模式等。

圖4 可配置FIFO 控制器IP 軟核框圖

3.3 協議芯片綜合

Verilog HDL 程序通過Lattice 公司的CPLD 開發軟件ispLEVER 7.0 進行編譯、綜合,多次嘗試后最終選擇了Lattice 公司MachXO 系列CPLD 中的MachXO2280 芯片, 綜合后的主機協議芯片占用CPLD 資源的60%左右, 從機協議芯片占用CPLD資源的45%左右,FIFO 控制器充分利用了MachXO2280芯片內部的嵌入式RAM 塊, 同時利用了鎖相環實現高頻率的時鐘工作。最后通過LSC ispVM(R)System 燒寫軟件經JTAG 口下載到CPLD 芯片中進行協議芯片功能驗證測試。

4 結語

本文設計的背板總線協議芯片在背板串行總線時鐘頻率為25MHz、信號電平為LVTTL,底板引線長度為40cm,1 臺主機連接3 臺擴展模塊的情況下工作穩定并通過了群脈沖試驗,驗證了這一組協議芯片的設計是成功的。由于該組協議芯片是針對PLC 的周期性和非周期性數據傳送專門設計的,硬件實現的協議幀控制器支持高速率通信、支持數據幀檢驗功能,避免了數據傳送的錯誤,大大降低了外圍單片機的軟件開銷,增強了可靠性,是一組非常適合用于PLC 背板總線或者需要多模塊協同工作的背板總線系統協議芯片。

評論