MC8051 IP核基本結構及原理

1 MC8051功能特點

采用完全同步設計:指令集和標準8051微控制器完全兼容;指令執行時間為l~4個時鐘周期,執行性能優于標準805l微控制器8倍左右;用戶可選擇定時/計數器、串行接口單元的數量,最多可增加到256組;新增特殊功能寄存器用于選擇不同的定時/計數器、串行接口單元;可選擇是否使用乘法器(乘法指令MUL);可選擇是否使用除法器(除法指令DIV);可選擇是否使用十進制調整功能(十進制調整指令DA);I/0口不復用,無雙向數據I/O端口,輸入、輸出端口獨立;內部帶256Byte RAM;⑾最多可擴展至64 KB的ROM和64 KB的RAM;與工藝無關,可通過修改VHDL源代碼擴展及參數化設置。

2 MC8051結構及設計層次

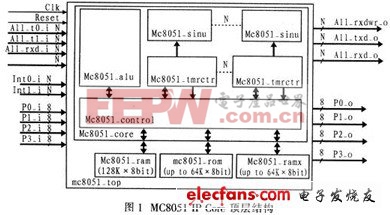

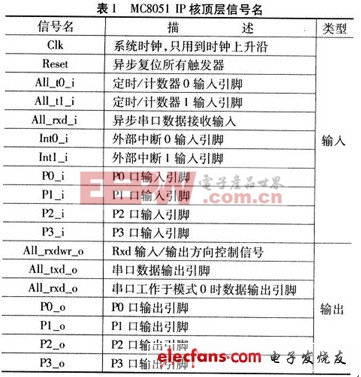

圖1給出MC805l_eore的頂層設計模塊及其子模塊,包括頂層的各個信號端口及3個存儲器模塊。同時給出了頂層的輸入輸出I/O口。定時/計數器和串行接口單元,對應于圖中的MC805l_tmrctr和MC8051_siu模塊,數量可選擇,圖中用虛線表示。MC8051 IP核與工業標準8051單片機不同,MC8051的輸入、輸出并口分別映射到獨立的端口上。其頂層各I/O信號的描述如表l所示。

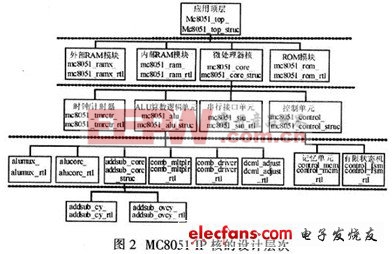

MC805lIP核的設計層次及對應的VHDL文件如圖2所示嘲。它由定時/計數器、ALU算數邏輯單元、串行接口單元和控制單元組成。RAM及ROM模塊不包括在IP核內,處于設計的頂層,方便于不同的應用設計及仿真。

圖2中,最頂層是用戶的實際應用設計模塊,它將ROM、RAM及mc8051_core封裝在內部。實際應用中用戶可添加自定義附加邏輯模塊,與設計層次中的RAM、ROM模塊處于同一個層次。

評論