多核DSP兼具ASIC和FPGA特性概述

由于ASIC解決方案NRE成本高,產品開發周期較長,在支持各種不同無線標準升級上靈活性不足。而FPGA的功耗對于高速、復雜運算而言要比ASIC和DSP加速器更高,同時在快速開發和調試上也難達到理想狀態。基于此,TI近日針對無線基礎設施應用而推出的DSP解決方案 SoC架構,基于C64x+多核DSP兼具ASIC處理能力和FPGA的靈活性,從而適應3G和4G無線基礎架構設備制造商對高性能芯片的需求。

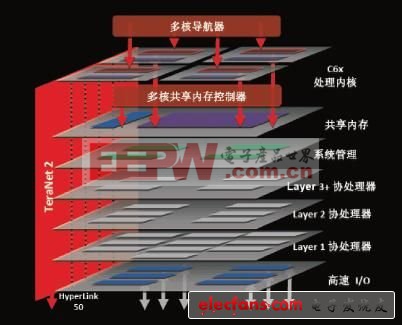

具有高度靈活性的可編程解決方案,同時兼具ASIC方案的優化特性,是TI面向無線基礎設施市場開發的新一代DSP多核架構。基于40nm工藝的全新DSP架構主要特性包括:多核DSP可實現1.2GHz工作頻率;增加的浮點支持4G多變量控制系統開發,可輕松實現對時間區隔和分頻制的支持;全新多核導航器可實現DSP核、硬件加速器間數據的準確轉移,同時提供帶50Gbps的非封鎖交換機架構外設,無需使用系統模塊而滿足了未來4G系統的要求;穩定的工具套件、針對具體應用的軟件庫和平臺軟件,為用戶縮短開發周期提供更有效的調試和分析;運行頻率高達1.2GHz、引擎性能為256 GMACS和128 GFLOPS的TI全新DSP架構實現了DMS性能5倍提升,同時將平均內核存儲增加了2倍,保證了應用性能的穩定;提供高性能1層、2層網絡協處理器。

全新SoC架構多核導航器(Multicore Navigator),利用8192任務型隊列優化數據流的片上網絡管理單元,支持內核與存儲器存取之間的直接通信,省去了外設存取從而充分釋放出多核性能。通過抽取可能影響多核系統中軟件開發的諸多細節,極大地簡化了程序模型。由于每個DSP內核均集成定點與浮點處理功能,通過提供內核間、硬件加速器間以及外設間的自動路徑設置,每個內核彼此都可以不受核間沖突影響而獨立工作,通常能為設計工程師節省3個月時間。多核共享存儲器控制器設計方案,可加快片上及外接存儲器存取速度;新架構還支持內核間動態系統調度并支持全內核授權,使得多核架構能類似于性能強大的單核系統。

這些適用于無線基站的4核器件,以及適用于媒體網關與網絡應用的8核器件,TI預計將于 2010 年下半年開始提供樣片。

評論