淺談低電壓低靜態電流LDO的電路設計

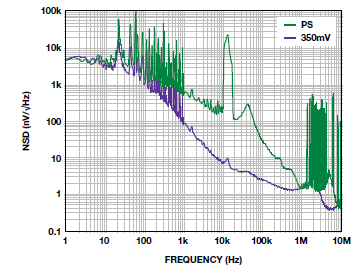

摘要:設計一種低電壓低靜態電流的線性差穩壓器。傳統結構的LDO具有獨立的帶隙基準電壓源和誤差放大器,在提出一種創新結構的LDO,把帶隙基準電壓源和誤差放大器合二為一,因而實現了低靜態電流消耗的目的。設計采用CSMC0.5 μm 雙阱CMOS工藝進行仿真模擬,這種結構LDO在輕負載情況下靜態電流僅為1.7 μA,輸出暫態電壓最大變化為9 mV.

隨著過去幾十年里掌上智能終端快速發展,低壓差的線性穩壓器(Low Drop-out Regulator,LDO)因其具有低功耗、高的電源抑制比、體積小、電路設計簡單等優點得到大量應用。LDO大部分時間工作在低負載應用,因此,其在低負載情況下的靜態電流消耗決定著電池的壽命。當今的LDO發展趨勢是低電壓、低靜態電流來延長電池使用壽命。然而,低靜態電流會導致不穩定性,帶來大的輸出電壓暫態變化,必須在靜態電流和輸出暫態特性進行合理的折中。相比于傳統LDO采用分立結構的帶隙基準電壓源和誤差放大器,本文給出一種創新結構的LDO,將帶隙基準電壓源和誤差放大器兩個模塊合二為一,因此更容易實現低靜態電流消耗,低暫態電壓變化。

1 LDO電路分析

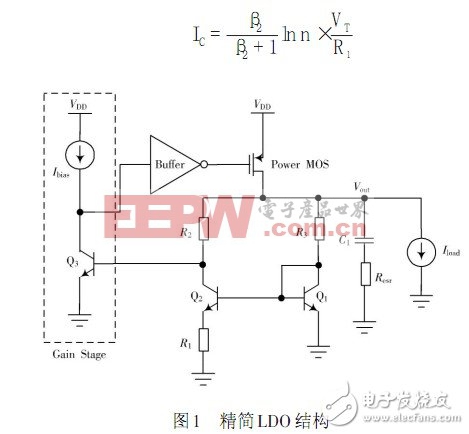

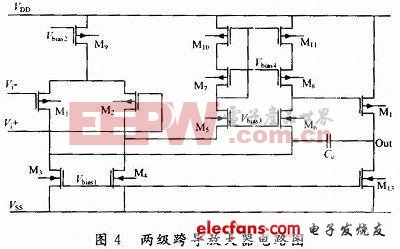

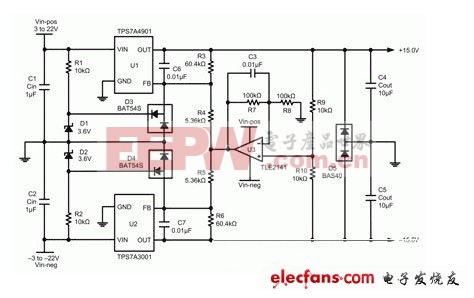

圖1給出精簡結構的LDO,僅僅包括4條主要的電流支路,分別是:增益級、緩沖級和2個PTAT電流源。

相比傳統結構LDO,精簡結構將帶隙基準電壓源和誤差放大器合二為一,因此在其他性能不變情況下,可將電路靜態電流消耗減小到原來1 2 左右。

這個電路存在兩個缺點:輸出電壓為帶隙基準電壓不可調;需要使用NPN晶體管,而標準CMOS工藝中并不存在NPN晶體管。由于如今的SoC趨向工作在低電壓環境,因此這種結構能夠有充足的應用場合。第二個問題在單片設計時候,采用雙阱CMOS工藝,只需增加一道掩膜工藝,費用增加不多,因此兩個問題實際應用并不明顯。

1.1 帶隙基準電壓分析

三極管基射級電壓和熱力學電壓分別具有負、正溫度系數,因此帶隙基準電壓的原理是疊加三極管基射級電壓和熱力學溫度電壓,達到在室溫下的零溫度系數。

在精簡LDO結構中,晶體管Q3和電阻R2定義帶隙基準電壓,流過R2為PTAT電流。通過鏡像流過晶體管Q1電流。晶體管Q3偏置到集電極電流。因此,在環路中,晶體管Q1和Q3將調整到相同的基射級電壓值。尤其環路比較高的情況下,這種調整是相當精確的。因此,通過合理設計電阻R2和R3,晶體管Q1,Q2和Q3有相同的集電極電流。因此:

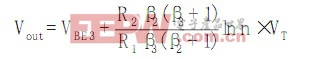

式中:IS 是三極管飽和電流;β2 是晶體管Q2的電流增益;n 是晶體管Q2和Q1射級面積比。通過式(1)可以得到PTAT電流:

因此通過晶體管Q3的基射級電壓和R2電壓疊加即可得到輸出電壓值:

調整電阻比值,使VT 系數 值為17.2,即可得到溫度系數為零的帶隙基準電壓。

值為17.2,即可得到溫度系數為零的帶隙基準電壓。

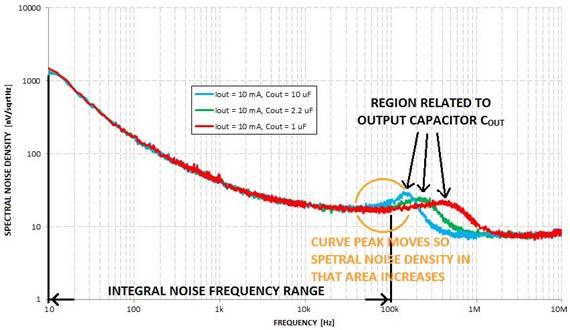

1.2 LDO頻率分析

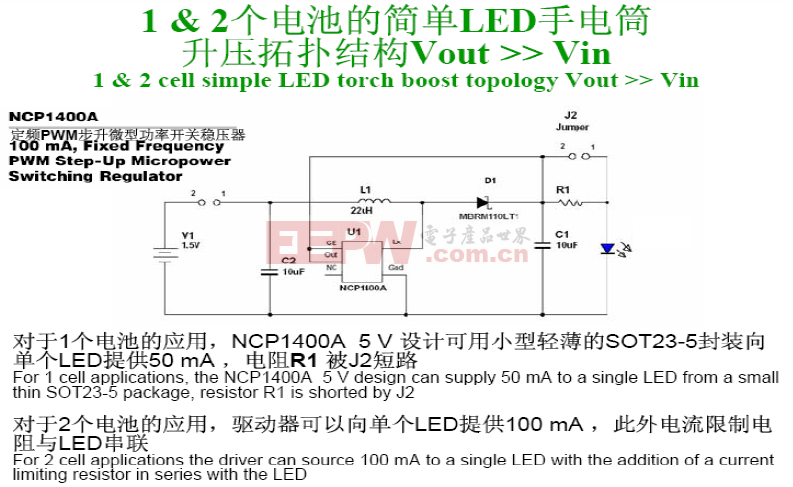

評論