基于FPGA的基帶64×64數據分配矩陣設計方案

3.2 FPGA內部編程

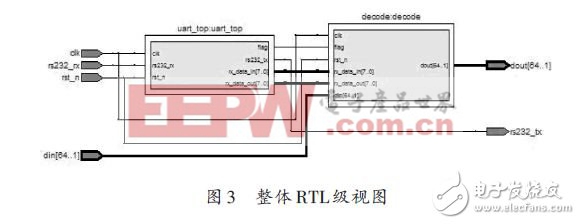

FPGA模塊的主要功能是實現串口收發和譯碼,相應地在用Verilog HDL實現時也分為串口收發和譯碼2個電路模塊,經綜合后其RTL級視圖如圖3所示。開發工具采用Altera公司推出的集成EDA 開發工具Quartus Ⅱ,可以完成Altera公司所有的FPGA /CPLD產品開發的設計輸入、綜合、實現等環節。

3.2.1 串口收發模塊設計

串口收發模塊就是圖3中的uart_top模塊,主要負責串行數據的接收與發送,并將接收到的數據送入下一級。

該模塊的功能已通過串口調試工具調試成功。該模塊由4個子模塊構成,分別為控制接收波特率的speed_rx模塊、控制發送波特率的speed_tx 模塊、數據接收模塊my_uart_rx、數據發送模塊my_uart_tx.

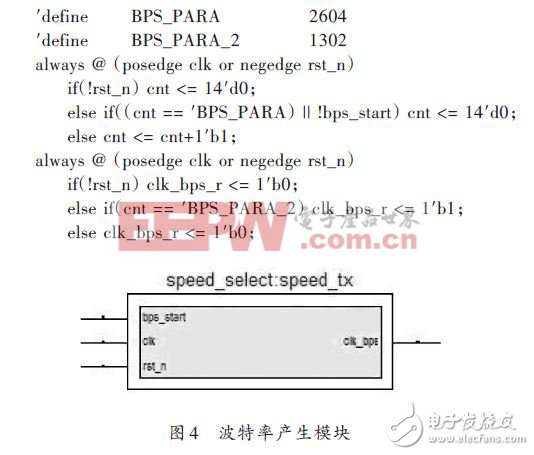

接收、發送波特率的控制可以引用同一模塊的發送來實現。其模塊化框圖如圖4所示,當檢測到輸入信號 bps_start出現一個上升沿后,則該模塊通過計數來實現分頻,例如時鐘頻率為25 MHz,波特率為9 600,則計數周期的25 000 000/9 600≈2 604,該模塊部分代碼如下:

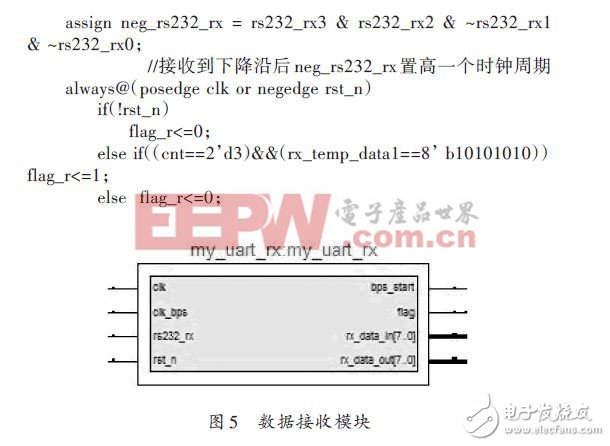

數據接收模塊的模塊化框圖如圖5所示,它是通過移位運算來接收串行數據,如檢測到rs232_rx 由高電平變為低電平則開始移位接收數據,每次接收3 B 的數據,將第二、第三個字節輸入下一級,若檢測到第一個字節為10101010(即16進制的AA),標志信號flag就將維持一個周期的高電平輸出,否則flag一直維持高電平,那么后級將無法鎖存第二、第三字節。部分代碼如下:

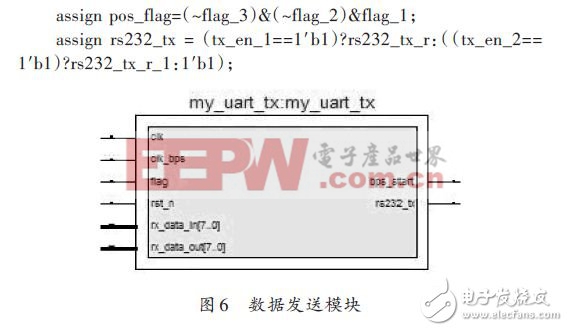

數據發送模塊是用來返回接收數據讓上位機進行糾錯的,其模塊化框圖如圖6所示。如檢測到flag變為高電平時,鎖存輸入的兩個字節返回給上位機,部分代碼如下:

3.2.2 譯碼模塊設計

譯碼模塊的模塊化框圖如圖7所示,其功能是對上位機發送的輸入輸出端口編號進行譯碼,使相應的輸入端口和輸出端口連通,如檢測到flag 有效的情況下,rx_data_in為2,rx_data_out為3,則該模塊會將din[2]通道的輸入信號經dout[3]輸出通道輸出。部分代碼如下[10]:

![則該模塊會將din[2]通道的輸入信號經dout[3]輸出通道輸出。部分代碼如下[10]:](http://editerupload.eepw.com.cn/fetch/20131227/205066_2_4.jpg)

3.2.3 譯碼模塊仿真

評論