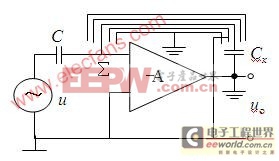

利用運算放大器式電路虛地點減小電纜電容原理圖

采用運算放大器法

下圖是利用運算放大器的虛地來減小引線電纜寄生電容CP的原理圖。圖中電容傳感器的一個電極經電纜芯線接運算放大器的虛地Σ點,電纜的屏蔽層接儀器地,這時與傳感器電容相并聯的為等效電纜電容Cp/(1+A),因而大大地減小了電纜電容的影響。外界干擾因屏蔽層接儀器地,對芯線不起作用。

傳感器的另一電極接大地,用來防止外電場的干擾。若采用雙屏蔽層電纜,其外屏蔽層接大地,干擾影響就更小。實際上,這是一種不完全的電纜“驅動技術”,結構較簡單。開環放大倍數A越大,精度越高。選擇足夠大的A值可保證所需的測量精度。

圖5.3-12 利用運算放大器式電路虛地點減小電纜電容原理圖

電子管相關文章:電子管原理

評論