SPI4.2總線應用和調試

SPI4.2總線(System Packet Interface,系統間數據包接口)是一種速度高達10 Gb/s的芯片間互連總線,主要應用于ATM信元傳輸、POS(Packet Over SONET/SDH,基于SONET/SDH的包傳輸)和10 Gb/s以太網等高端場合。特別在通信領域,很多高端處理器和網絡處理器,如Intel公司的IXP2800、Cavium公司的多內核處理器CN58xx系列、NetLogic公司的XLR732、Broadcom的BCM1480,幾乎都集成了SPI4.2接口,以提高芯片的吞吐能力,適應通信產業朝著LTE(長期演進)發展的需求。還有眾多的物理層芯片,例如Cortina公司的CS1331,可以將SPI4.2總線轉換成8個千兆以太網接口。SPI4.2總線之所以被眾多的高端芯片所采用,與其高速、靈活、可靠的特性是密不可分的。

1 SPI4.2總線基本原理

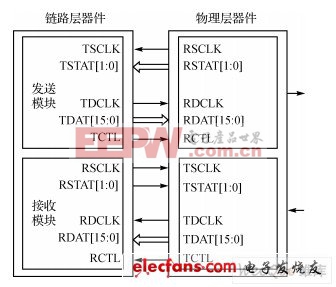

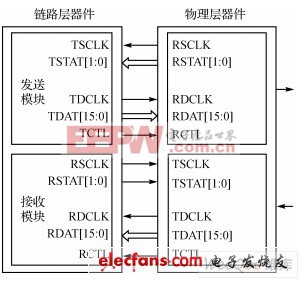

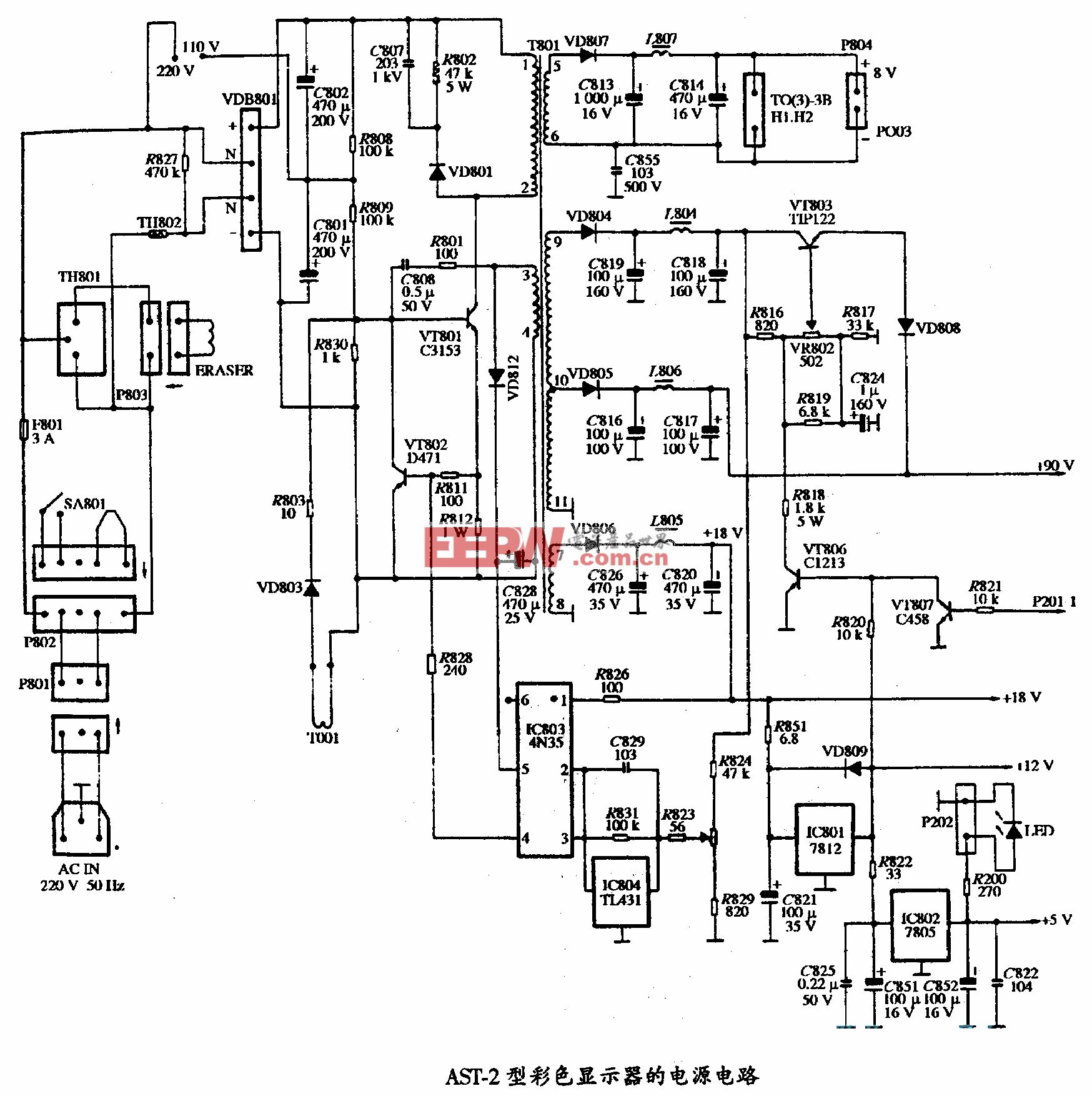

SPI4.2總線是一種芯片間的互連總線,連接芯片的鏈路層和物理層模塊。其工作時鐘是源同步雙邊沿觸發時鐘,至少為311 MHz。圖1是使用SPI4.2總線連接兩個芯片的示意圖。可見,SPI4.2總線的信號在發送和接收方向完全對稱而又互相獨立,數據鏈路和狀態鏈路分開,并且其時鐘也是完全分開的。因此,該總線不僅適合于雙向通道,而且適合于只收不發或者只發不收的單向通道。

圖1 SPI4.2連接示意圖

SPI4.2總線具有以下特點:

① 點對點互連,收發數據鏈路寬度為16位。

② 發送和接收模塊的信號各分為兩組,即數據信號和狀態信號,分別對應數據鏈路和狀態鏈路,每個鏈路具有自己的時鐘。數據鏈路發送和接收數據,狀態鏈路傳輸相應鏈路的狀態信息。

③ 數據鏈路包含DCLK、DAT[15:0]和CTL三種LVDS(低壓差分傳輸)信號。前面加“T”表示信號屬于發送模塊,加“R”表示信號屬于接收模塊。以發送模塊為例,TDCLK是雙邊沿觸發時鐘,TCTL是控制信號,TDAT[15:0]承載了數據和控制信息。當TCTL為高電平時,TDAT[15:0]傳送的是數據包;當TCTL為低電平時,TDAT[15:0]傳送的是控制包。數據采用DIP4校驗交織碼。

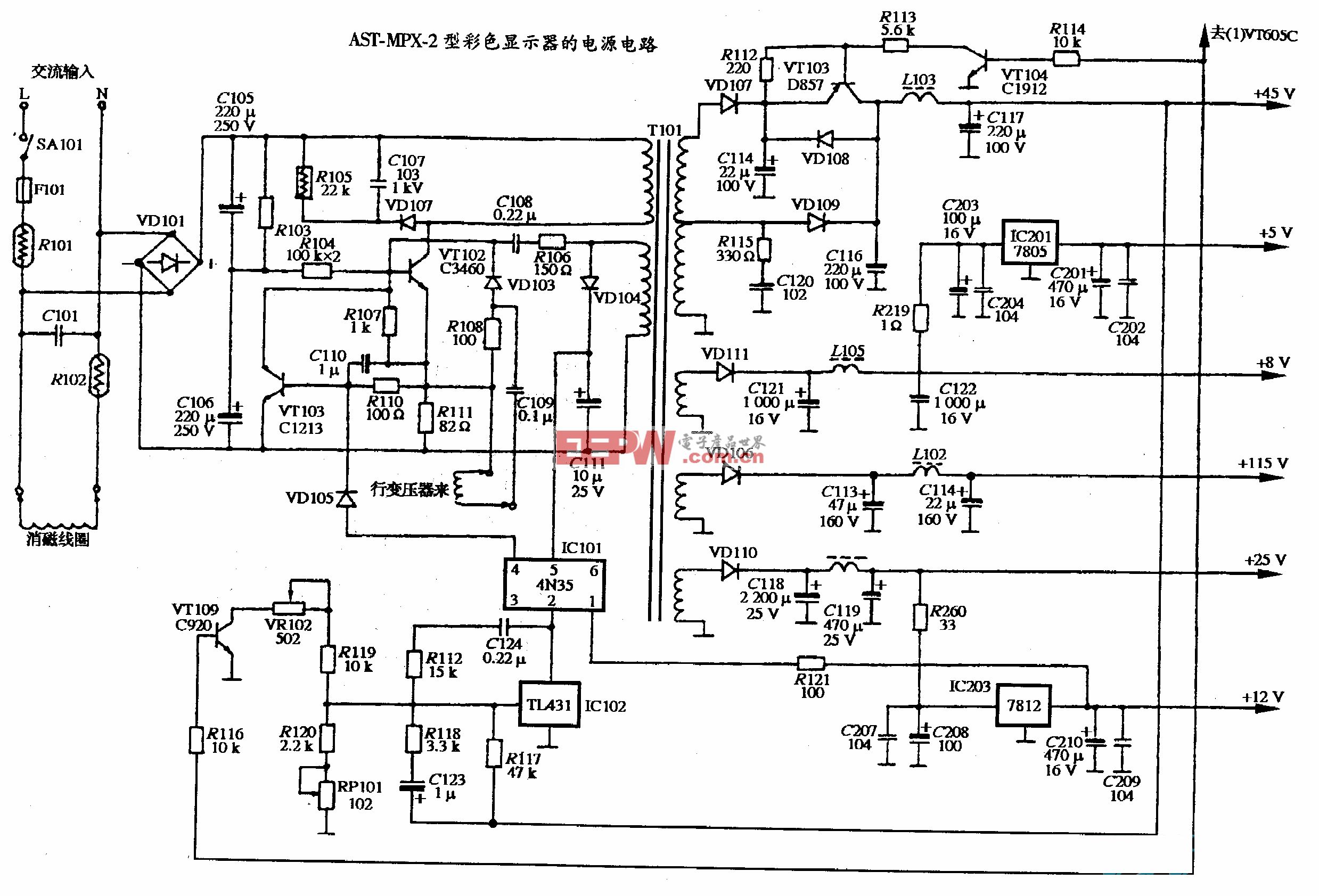

④ 狀態鏈路包括SCLK時鐘信號和STAT[1:0]狀態信號,信號類型是LVTTL或LVDS。SPI4.2 發送時序如圖2所示。如果選擇LVTTL,則SCLK時鐘頻率是數據鏈路時鐘速率的1/4。如果選擇LVDS,則SCLK時鐘頻率和數據鏈路時鐘頻率相同。下文中均以LVDS為例進行闡述。狀態鏈路主要用于流控。

⑤ 接收和發送模塊都含有一個FIFO隊列,用于緩存數據,隊列長度由芯片設計而定。隊列的狀態信息通過狀態鏈路周期性地發送,接收模塊和發送模塊的狀態信息是獨立的。狀態信息附加了DIP2交織校驗碼,以提高傳輸可靠性。

圖2 SPI4.2 發送時序

評論