最詳盡32位MCU低功耗設計考量與經典范例參考(二)

制程選擇

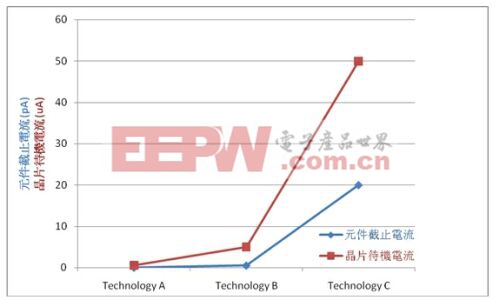

為了達到低功耗的運作,并能有效地在低耗電待機模式下,達到極低的待機功耗,可以透過對制程的選擇而站上基本的要求門檻。在不強調速度極致的某些制程分類,選擇極低元件截止電流制程(如下圖)進行邏輯閘制作,并進行數位設計是方法之一。選擇這種策略的額外效益是,通常也能在降低動態操作電流上,達到較佳的表現。另外,由于高溫大幅增加靜態電流,當溫度由攝氏25度增加到攝氏 85度時,一個典型比例約增加 10 倍的靜態電流,以非低功耗 0.18 微米制程開發的 32 位元 MCU,邏輯閥門數 200K、4KB SRAM 在核心電壓 1.8V、攝氏25度的靜態耗電約為 5 ~ 10 微安,當溫度升高到攝氏 85度時,靜待電流將會飆高到 50 ~100 微安。而低功耗制程在攝氏85度僅約 10微安靜態電流。

低功耗高效能的 CPU內核

早期低功耗 MCU 受限于成本及制程技術,大都選擇 8 位元 CPU 內核,但隨著工業上的智能化也在展開,如遠端監控,數位化、網路化等。簡單說來,就是人物之連結(云端應用)、物物之連結(物聯網) 需求越來越多,導致產品功能越來越復雜,運算量越來越高,8 位元 MCU 已逐漸無法滿足效能需求。 為了兼顧低功耗高效能,選擇適用的 32 位元 CPU 內核乃大勢所趨。

選擇低功耗CPU 內核,除了單位頻率耗電流外,還需要綜合考量緊湊的低記憶體代碼,相同功能所需的代碼越長,除了增加記憶體成本,也代表更長的運行時間及功耗。另外,由于軟件開發成本在后期將會越來越高,大量的參考代碼及更多的第三方開發商的支持,都可以有效降低軟件的開發時間及成本。所以選擇一款更多人使用的 CPU 內核也是重要的考量之一ARM Cortex-M0閥門數僅 27K,使用的電量在 1.8V,超低泄漏 180ULL (Ultra LowLeakage) 僅約50μA/MHz。M0 內核采用Thumb2指令集架構,產生出非常緊湊的低記憶體代碼,進一步降低了電源需求。ARM自 2009 年發表了32位元Cortex-M0內核以來,包括 NXP、新唐科技、ST、Freescale等多家國內外 MCU 大廠相繼投入Cortex-M0 MCU 開發,不論供貨或者品種的齊全度都已十分成熟,投入Cortex-M0的 MCU 開發商也在持續增加中。

低功耗數位電路

對于一般的同步數位電路設計,要使數位單元有效降低操作電流,透過控制時鐘的頻率或截止不需要的時鐘跳動,也是重要的方法。低功耗MCU通常配備豐富的時鐘控制單元,可對各別的數位周邊單元,依照需求做降頻或升頻的操作調整,在達到運作能力的同時,用最低的頻率來運行。但為了達到更彈性的時鐘源配置,可能導致 CPU 內核和周邊電路時鐘不同步的現象,此時必須仔細考慮電路設計,保證跨時鐘領域資料存取的正確性。

另外為了盡量降低 CPU介入處理時間或降低 CPU 工作頻率而節省下來的功耗,可以提供 DMA 或周邊電路相互觸發電路進行資料的傳遞,例如Timer 定時自動觸發 ADC 或 DAC,并透過 DMA 進行資料由 ADC 到 RAM 或者 RAM 到 DAC 的搬移,同時在 ADC 的輸入可以增加簡單的數字綠波及平滑化電路,如此不須要 CPU 經常介入處理,也不會因為需要即時處理 ADC 或 DAC 事件導致中斷程序占用太多時間,降低系統的實時性及穩定性。

支援多種工作模式

為了配合不同的應用需求,并達到系統平均功耗的最小化,低功耗 MCU需要提供多種操作模式,讓使用者靈活調配應用,常見的操作模式有下列數種:

正常運行模式:CPU 內核及周邊正常工作,能即時改變 CPU 及周邊的工作頻率 (On the Fly) 或關閉不需要的時鐘源以獲得最佳的工作效能。

評論