一種16位高速數模轉換器(DAC)的設計與實現

整體測試結果和電路概貌

本文引用地址:http://www.j9360.com/article/203231.htm基于0.25微米混合信號CMOS工藝技術,并采用上述自校準電路設計方案,我們完成了一個采用分段式電流舵結構的16位400MSPS的D/A轉換器芯片的版圖設計,如圖5所示,該電路芯片尺寸為4.9×4.9mm2,整個DAC電路一共有110個壓焊塊。目前該電路已經成功完成工藝流片,電路測試評估板的實物照片如圖6所示。

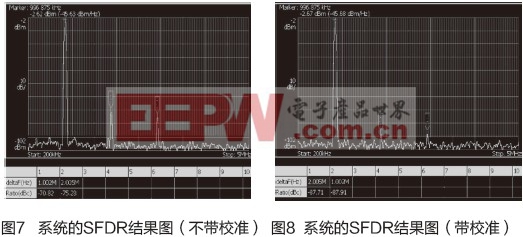

對封裝后的DAC電路進行的初步測試結果表明,該DAC電路工作正常。圖7為系統不帶校準的實測SFDR,圖8為系統帶校準后的實測SFDR。可見經過自校準后,電路的SFDR提升了十幾個dB,并且諧波也明顯減小。

我們對該DAC芯片還進行了其它各項指標的測試,電路在400MHz時鐘頻率下經過自校準后的測試結果如下表1所示。由表中各項測試數據可見,該芯片的各項性能參數指標優異,表明整個DAC芯片的性能良好。

總結

基于0.25微米Mixed-Signal CMOS制造工藝,本文設計并實現了一個高速高精度單片集成化的數模轉換器(DAC)。論文中的DAC電路采用分段式電流舵結構,其時鐘的采樣頻率為400MHz,分辨率為16Bit。電路設計中還采用了電流校準技術,既保證了DAC電路的高精度,也減小了梯度誤差的影響。實際流片后的測試結果表明,自校準技術的采用可使DAC

電路的精度和性能得到大幅度的提升,芯片的輸出諧波也明顯減小。本DAC產品是我們在高速高精度DAC電路研制方面的一次嘗試,它的研制成功為我們今后研制開發性能更加優異的數模轉換器產品打下了良好的技術基礎。

參考文獻:

[1] Jose Bastos, Augusto M. Marques, Michel S. J.Steyaert and Willy Sansen. A 12-Bit Intrinsic Accuracy High-Speed CMOS DAC[J]. IEEE Journal of Solid-State Circuits, 1998, 33, (12):1959-1960

[2] Chi-Hung Lin and Klaas Bult. A 10-b, 500-M,sample/s CMOS DAC in 0.6mm2[J]. IEEE Journal of Solid-State Circuits, 1998, 33, (12):1948-1957

[3] 趙耀華,陸鐵軍,王宗民.基于VLSI的高速LVDS接口電路設計[J].微電子學與計算機,2009,26,(11):78-81

[4] A.R Bugeja, B. Song. A 14b, 100Ms/s CMOS DAC Designed for Spectral Performance[J]. IEEE Journal Solid-state Circuits, 1999,34:1719-1731

[5] A.R Bugeja, B. Song. A Self-trimming 14b, 100Ms/s CMOS DAC[J]. IEEE Journal Solid-state Circuits, 2000,35:1841-1852

評論