AT24系列存儲器數據串并轉換接口的IP核設計

關鍵詞 I2C總線 AT24系列存儲器 VHDL 串并轉換 微處理器??

1 I2C總線的基本概念?

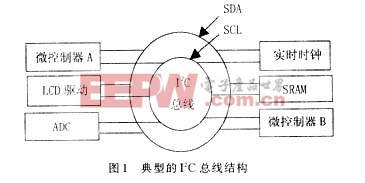

I2C總線協議是Philips公司推出的總線協議。它是多主機總線,通過2根線(SDA-aserial data line,SCL-a serial clock line)與連接到總線上的器件之間傳送信息,根據地址識別每個器件。例如,微控制器、LCD驅動器、存儲器、鍵盤,連接的器件可以工作在發送和(或)接收狀態。很顯然,LCD驅動器等一些器件只能是接收器,而存儲器可以發送和接收數據。對于AT24系列存儲器來說,器件的地址是通過把地址輸入端A0,A1,A2進行硬件連接來確定的。

? 圖1是典型的I2C總線結構。SDA和SCL都是雙向線,通過上拉電阻接正電源。當總線空閑時,這兩根線處于高電平狀態,連到總線的器件的輸出級必須是開漏極或集電極開路,以具有線“與”的功能。設備與總線的接口電路如圖2所示。 ?

????????

2 I2C總線的數據傳輸?

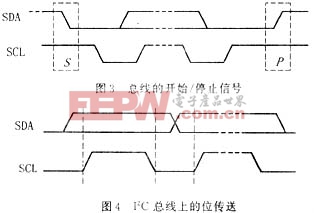

在I2C總線的數據傳輸過程中,定義了開始和停止信號。如圖3所示,SCL保持“高”,SDA由“高”變為“低”為開始信號;SCL保持“高”,SDA由“低”變為“高”為停止信號。開始(S)和停止(P)信號由主器件產生。在時鐘高電平期間上的數據必須保持穩定,如圖4所示,只有在時鐘線SCL的時鐘低電平期間,SDA線上高電平或低電平才能變化。

?

?

?

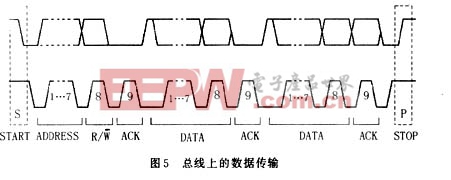

到SDA線上的每個字節必須是8位長度,每次傳輸的字節數是不受限制的,每個字節后面必須跟一個響應位。如果一個接收器件在完成其他功能前(如一個內部中斷)不能接收另一個數據的完整字節時,可以使時鐘保持低電平,以促使發送器進入等待狀態。當接收器準備好接收下一個數據字節并釋放SCL線,數據傳輸繼續進行。圖5表示出了I2C總線上的數據傳送時序。

數據傳送具有應答是必須的。與應答對應的時鐘脈沖由主控器件產生。發送器在應答期間必須下拉SDA線。當尋址的被控器件不能應答時,數據保持為高,于是主器件產生停止信號終止傳輸。?

3IP核的設計

3.1該IP核設計與軟件實現的比較

? 在I2C總線的應用中,實現微機與AT24系列存儲器之間的通信,可以把微機的通用I/O口作為I2C總線的接口,通過匯編由軟件控制實現數據的傳輸。由于軟件在操作上時間的原因,速度總要受到限制。并且匯編控制也很難作為一個統一的標準在應用中推廣。通過IP核設計,我們可以在硬件上實現數據串并轉換的目的。工作的速度只與存儲器本身的特性有關,克服了軟件在此方面的不足。

3.2系統設計方案

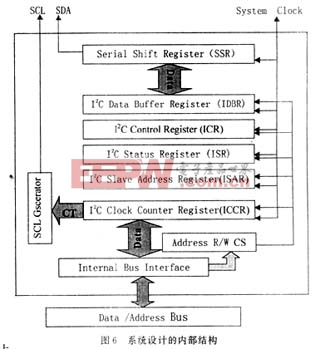

? 該系統主要由I2C串行移位寄存器(SSR)、數據緩沖寄存器(IDBR)、控制寄存器(ICR)、狀態寄存器(ISR)、從地址寄存器(ICCR)、SCL產生器(SCL Generator)及其他總線組成。圖6為其基本內部結構。

? 在該系統中,SSR把并行數據變為串行數據,傳輸給存儲器,或者把存儲器的串行數據變為并行數據,傳輸為處理器;IDBR把并口來的數據或把被轉換成并行的數據暫且裝載起來;ICR控制著整個系統的讀/寫、數據的轉換等操作;ISR則監視著系統的狀態。

3.3數據的通信格式

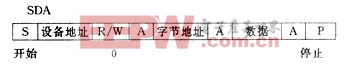

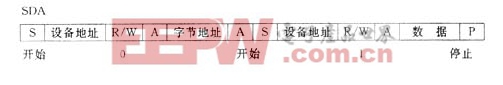

? 主控制器(CPU)如果要從存儲器讀數據或者寫(0表示寫)數據到存儲器,則需經過接口轉換。SDA上的信號傳輸要遵循一定的格式。在主控制器(CPU)給存儲器寫數據時,把設備地址、字節地址和數據送給接口,接口完成與存儲器之間的數據交換。如下:

?

其中確認(A)是存儲器傳送給接口的信號,其余的如開始(S)、設備地址等信號是接口產生的信號。

???????????????

?

主控制器從接口讀數據時,會把設備地址、字節地址和讀信號告訴接口,接口通過與存儲器進行數據交換,把數據讀出來,送給主控制器。數據格式如下:

其中確認(A)和數據是存儲器產生的,其余的如開始(S)、設備地址、停止(P)等信號是接口產生的。

3.4IP核的VHDL設計

? 該IP核的VHDL設計從低到高共5個模塊。這幾個模塊分別為頭地址移位寄存器模塊、數據移位寄存器模塊、計數器模塊、控制模塊和外圍綜合模塊。

? 頭地址移位寄存器是用來裝載寫入(讀出)設備地址,在控制模塊的控制下,把設備地址移位到串行數據線SDA上。數據移位寄存器是用來裝載寫入/讀出的數據、字節地址,并在控制模塊的控制下,把寫入的數據、字節地址移位到SDA上,或者把從SDA讀出的串行數據變為并行數據,以傳送給主控制器。在該IP核設計中,需要對移位的數據字節進行記數,計數器模塊實現該功能。控制模塊主要通過以剛提到的三個模塊為基礎,實現了數據的單向傳輸,也就是把雙向的數據線分成2根單向的數據線來傳輸數據。而外圍綜合模塊則把2根單向的的數據線綜合成一根雙向的數據線SDA,實現了接口的串并轉換功能。

3.5VHDL的實現與仿真

? 硬件描述語言VHDL(Very-high Speed IC Hard-ware Description Language)是一種用于電路設計的高層次描述語言,具有行為級、寄存器傳輸級和門級等多層次描述,并具有簡單、易讀、易修改和與工藝無關等優點。本設計采用MAX+plus Ⅱ 9.5 作為綜合工具,對設計的VHDL程序進行調試和波形仿真。

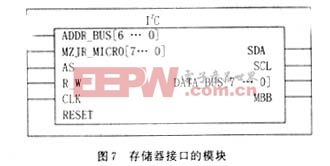

? 在調試中,MAX+plus Ⅱ生成所需要的I?2C接口模塊,如圖7所示,表示了整個接口的外部結構。

????

?

其中各個管腳的意義如下: ?

?

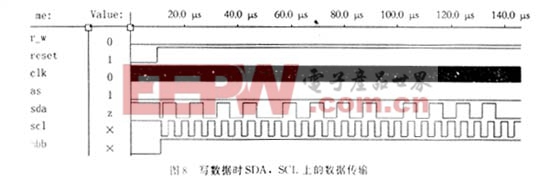

? 在仿真中,選擇EPF10K10LC84-3 作為下載芯片來實現模擬仿真。當向存儲器寫數據時,串行時鐘線和數據線得到圖8所示的仿真波形。

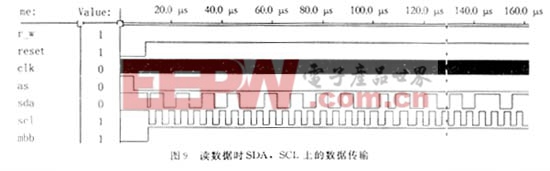

? 當從芯片中讀數據時,串行數據線和時鐘線上得到的仿真波形如圖9。

4結論

? 以上介紹了基于I?2C總線協議的AT24系列存儲

器數據串并轉換接口的VHDL設計,該接口是針對8位微處理器而設計的。基于FPGA技術的基礎上,把軟件仿真、編譯成功的程序,經JTAG電纜下載到以上指定的芯片上,用89C51與設計的接口進行數據通信,通過硬件驗證,能實現它應具備的功能,可在通信系統中得到運用。

參考文獻?

1于宏軍,趙冬梅.智能(IC)卡技術全書.北京:電子工業出版社,1996

2何立明.I2C總線應用系統設計.北京:北京航空航天大學出版社,1995

3王志華,鄧仰東.數字集成系統的結構化設計與高層次綜合.北京:清華大學出版社,2000

評論